CENTRO DE CIÊNCIAS EXATAS E DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# IMPLEMENTAÇÃO DE UMA API PARA EMULAR O KERNEL DE TEMPO REAL RTXC NO LINUX/GNU VISANDO APLICAÇÕES MULTICORE

**DANIEL SANT' ANNA CONSIGLIERI**

ORIENTADOR: PROF. DR. MARCIO MERINO FERNANDES

Co-Orientador: Prof. Dr. CÉLIO ESTEVAM MORON

São Carlos - SP Fevereiro/2017

CENTRO DE CIÊNCIAS EXATAS E DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# IMPLEMENTAÇÃO DE UMA API PARA EMULAR O KERNEL DE TEMPO REAL RTXC NO LINUX/GNU VISANDO APLICAÇÕES MULTICORE

#### DANIEL SANT' ANNA CONSIGLIERI

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Federal de São Carlos, como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação, área de concentração: Metodologias e Técnicas de Computação

Orientador: Prof. Dr. Marcio Merino Fernandes

São Carlos - SP Fevereiro/2017

CENTRO DE CIÊNCIAS EXATAS E DE TECNOLOGIA PROGRAMA DE PÓS-GRADUAÇÃO EM CIÊNCIA DA COMPUTAÇÃO

# Implementação de uma API para Emular o Kernel de Tempo Real RTXC no Linux/GNU Visando Aplicações Multicore

#### DANIEL SANT' ANNA CONSIGLIERI

Dissertação apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Federal de São Carlos, como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação, área de concentração: Metodologias e Técnicas de Computação.

Aprovado em: 01 de Fevereiro de 2017.

Membros da Banca:

Prof. Dr. Marcio Merino Fernandes

(Orientador – DC-UFSCar)

Prof. Dr. Prof. Dr. Célio Estevan Morón

(Co-Orientador – DC-UFSCar)

Prof. Dr. Alexandro Baldassin

UNESP - Rio Claro

São Carlos - SP Fevereiro/2017

Centro de Ciências Exatas e de Tecnologia Programa de Pós-Graduação em Ciência da Computação

#### Folha de Aprovação

Assinaturas dos membros da comissão examinadora que avaliou e aprovou a Defesa de Dissertação de Mestrado do candidato Daniel Sant Anna Consiglieri, realizada em 01/02/2017:

Prof. Dr. Márcio Merino Fernandes UFSCar

Prof. Dr. Célio Estevan Moron

**UFSCar**

Prof. Ør. Alexandro José Baldassin

UNESP

### **AGRADECIMENTO**

Ao meu pai Francisco Antonio Zanotto Consiglieri, pelo amor sem medida, por todo incentivo, apoio, paciência e conselhos fundamentais em minha formação A minha mãe Silvia Sant´Anna Consiglieri, Pela vida e por me ensinar bons valores.

Ao meu avô Zacarias Sant´Anna, por sempre me incentivar a aprender, dedicar nos estudos e ser um exemplo no saber

Aos meus irmãos

Bárbara Sant´Anna Consiglieri Val Magalhães,

Francisco Antonio Zanotto Consiglieri Junior e

Renata Sant´Anna Consiglieri

cunhado Eric Val Magalhães

e sobrinho Nathan Consiglieri Val Magalhães

por me ensinarem o significado de viver em família, amizade e apoio

A minha tia Eunice Margarida Consiglieri, por me incentivar, apoiar nos estudos, motivar a ser melhor e seus conselhos

Aos meus tios João Augusto de Sant´Anna Neto, Judite Mariano Sant´Anna, José Augusto Sant'Anna e Adriana Sant´Anna pelo incentivo e conselhos Ao Prof. Dr. Marcio Merino Fernandes,

por me ajudar a me tornar um pesquisador, por acreditar no meu potencial, pela paciência, pelos conselhos, por toda ajuda, conhecimento compartilhado e amizade.

Ao Prof. Dr. Célio Estevan Morón,

Por sempre estar disposto a ajudar, sendo um pai na pesquisa, pela paciência, pelos conselhos, pela parceria e co-autoria no desenvolvimento da API-RXTC-Linux, pelo conhecimento compartilhado e amizade.

Ao Prof. Dr. Alexandro Baldassin,

Pela participação como membro externo da banca examinadora, revisão da dissertação e proposta de correções.

Ao Prof. Dr. Hélio Crestana Guardia,

Pela participação na defesa, ajuda na revisão da dissertação e proposta de correções.

Ao meu amigo Antonio Ideguchi por me ajudar e incentivar a me dedicar nos estudos

A todos professores do Departamento de Computação responsáveis por minha formação

A todos funcionários, colegas, amigos do Departamento de Computação e da UFSCar

Ao CNPq pelo apoio financeiro através da bolsa de mestrado

Agradecimento in memorian

à minha bisavó Eunice Figueira,

às minhas avós Eunyce Zanotto Consiglieri,

e Nélia Therezinha Martinelli Sant´Anna

a minha tia-avó Délia Figueira Zanotto, Por sempre me ajudarem e torcerem por meu sucesso.

### **RESUMO**

O advento dos processadores multicore representou um grande avanço no desempenho da computação paralela. Os sistemas embarcados seguindo essa tendência, melhoraram o poder computacional disponível para sistemas de tempo real, possibilitando a utilização da cadeia de desenvolvimento GNU/Linux. Consolidado a mais de vinte anos no mercado, o RTOS RTXC da Quadros Systems, foi escolhido para ser emulado no ambiente Linux. Com o objetivo de se emular o kernel RTXC, a API-RTXC-Linux foi escrita em C e obteve resultados determinísticos além de distribuição homogênea para tempo de resposta das chamas implementadas, sendo possível seu uso para aplicações de tempo real.

Palavras-chave: emulador; sistema de tempo-real; sistemas embarcados; kernel RTXC; multicore;

## **ABSTRACT**

The advent of multicore processors represented a major advance in the performance of parallel computing. Embedded systems following this trend have improved the computing power available for real-time systems, enabling the GNU/Linux development chain. Consolidated to more than twenty years in the Linux environment. In order to emulate the RTXC kernel, an API-RTXC-Linux was written in C and obtained deterministic results as well as homogeneous distribution for the response time of implemented calls, being possible its use for real-time applications.

**Keywords**: emulator; real-time system; embedded systems; RTXC; kernel RTXC; multicore;

## LISTA DE FIGURAS

| Figura 2.1 - Representação arquitetura memória de acesso uniforme19                                                                |

|------------------------------------------------------------------------------------------------------------------------------------|

| Figura 2.2 - Representação arquitetura memória de acesso não uniforme20                                                            |

| Figura 2.3 - Representação da arquitetura de memória distribuída21                                                                 |

| Figura 2.4 - O STR reage a entrada do ambiente produzindo uma saída que afeta c<br>ambiente[Adaptada de (LABROSSE et al., 2008)]22 |

| Figura 2.5 - Organização lógica do Intel Core Duo. [Adaptado de:(LIN; SNYDER, 2009)]26                                             |

| Figura 2.6 - Organização lógica do AMD Dual Core Opteron.[Adaptado de: (LIN; SNYDER, 2009)]27                                      |

| Figura 2.7 - Diagrama lógico de Multiprocessadores Simétricos. [Adaptada de: (LIN; SNYDER, 2009)]29                                |

| Figura 2.8 - Arquitetura processador Cell31                                                                                        |

| Figura 2.9 - À esquerda um processo com um thread e a direita um processo multithreaded32                                          |

| Figura 2.10 - Esquema do modelo de passagem de mensagens34                                                                         |

| Figura 2.11 - Esquema de operação PGAS – [Adaptado de: (BARNEY, 2015)]36                                                           |

| Figura 2.12 - Ferramenta TotalView analisando código MPI [Extraído de: (BARNEY,2015)]40                                            |

| Figura 2.13 - Ferramenta Allinea DDT analisando código [Extraída de ("Allinea DDT")                                                |

| Figura 2.14 - Ferramenta Intel Parallel Studio XE [Extraída de ("Intel® Parallel Studio XE 2016") ]42                              |

| Figura 3.1 - Processador 8 núcleos Sandy Bridge-EP [Extraído de: (MOLKA et al., 2014)]44                                           |

| Figura 3.2 - Processador 16 núcleos Bulldozer. [Extraído de (MOLKA et al., 2014)].                                                 |

| Figura 3.3 – Estrutura e componentes do Cortex – A72 [Extraído de: ("Cortex-A72 Processor - ARM")]45                               |

| Figura 3.4 - Configuração Xenomai dual de kernel [Adaptada de: ("Start Here –<br>Xenomai")]49                                      |

| Figura 3.5 - Configuração de kernel unitária Xenomai. [Adaptada de: ("Start Here –<br>Xenomai")]50                                 |

| Figura 3.6 - Diagrama de blocos da arquitetura SimpleScalar [adaptado de: (AUSTIN et al., 2002)]51                                 |

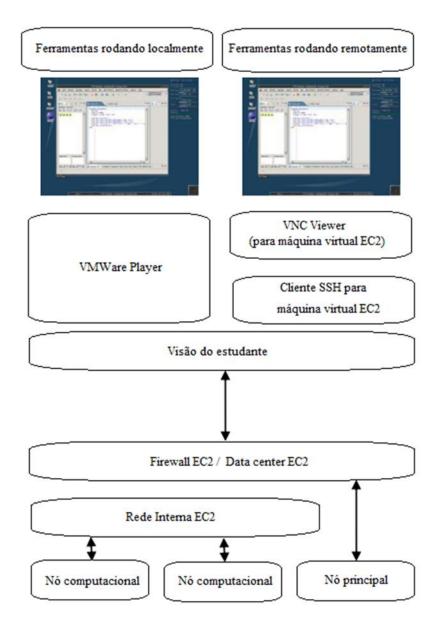

| Figura 3.7 - Arquitetura da solução StarHPC [Adaptado de (IVICA et al., 2009)]5                                                                                                                     | 52 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

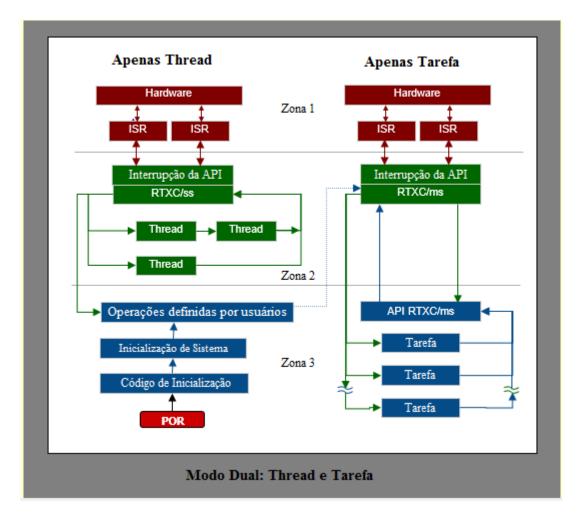

| Figura 4.1 - Zonas de Operação Quadros RTXC [Adaptado de: ("RTXC Quadros Manuals")]                                                                                                                 |    |

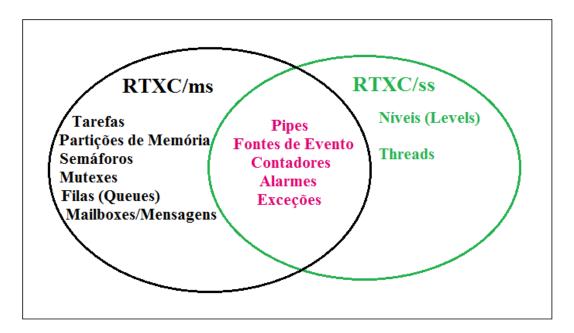

| Figura 4.2 - Esquema dos componentes RTXC/ms e RTXC/ss [Adaptado de: ("RTX Quadros Manuals")]                                                                                                       |    |

| Figura 4.3 - Exemplo de tabela de escalonamento [Adaptado de: ("RTXC Quadro Manuals")]                                                                                                              |    |

| Figura 4.4 - Primeiro exemplo de sequência de tempo Round-Robin. [Adaptado d<br>("RTXC Quadros Manuals")]                                                                                           |    |

| Figura 4.5 - Segundo exemplo de sequência de tempo Round-Robin. [Adaptado d<br>("RTXC Quadros Manuals")]                                                                                            |    |

| Figura 4.6 - Exemplo de escalonamento por prioridade. [Adaptado de: ("RTX Quadros Manuals")]                                                                                                        |    |

| Figura 4.7 - Hierarquia do gerenciamento de eventos. [Extraído de: ("RTXC Quadro Manuals")]                                                                                                         |    |

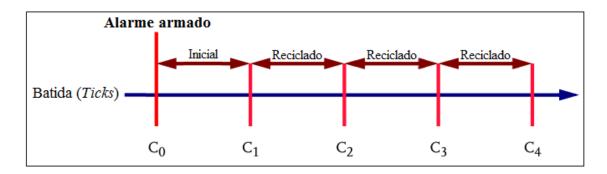

| Figura 4.8 - Mostra alarme sendo armado com valor de disparo inicial de $C_1$ - $C_0$ valor disparo reciclado $C_{n+2}$ - $C_{n+1}$ , para $0 \le n \le 2$ . [Adaptado de: ("RTX Quadros Manuals")] | (C |

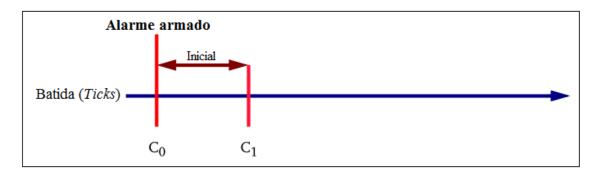

| Figura 4.9 - Alarme não-cíclico, armado com valor inicial de contador C <sub>0</sub> e disparand em C <sub>1</sub> . [Adaptado de: ("RTXC Quadros Manuals")]                                        |    |

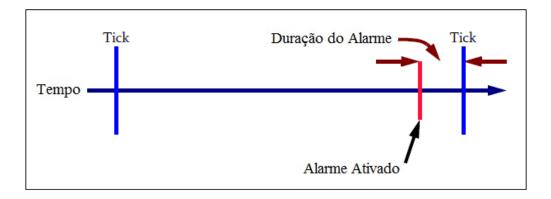

| Figura 4.10 - Duração de alarme não cíclico de tempo de duração um tick, situação [Adaptado de: ("RTXC Quadros Manuals")]                                                                           |    |

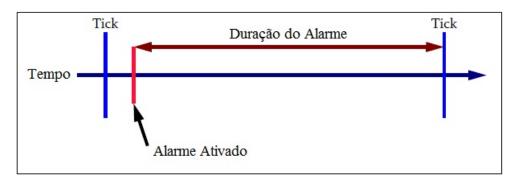

| Figura 4.11 - Duração de alarme não cíclico de tempo de duração um tick, situação [Adaptado de: ("RTXC Quadros Manuals")]                                                                           |    |

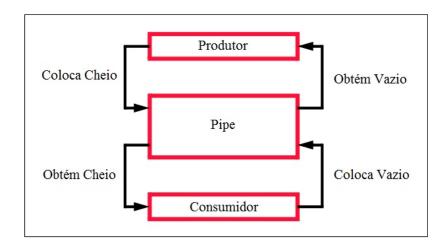

| Figura 4.12 - Operações básicas do Pipe [Adaptado de: ("RTXC Quadros Manuals"                                                                                                                       |    |

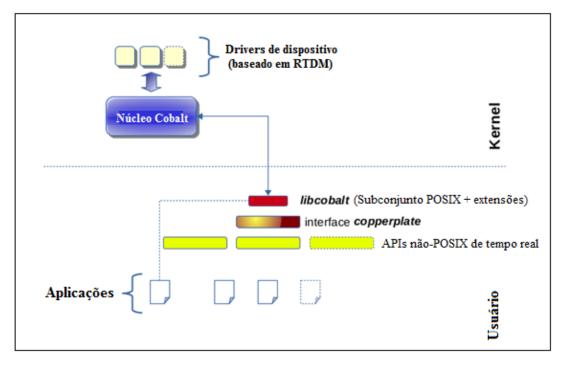

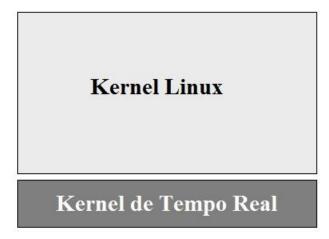

| Figura 5.1 - Modelo de Kernel Dual                                                                                                                                                                  | 73 |

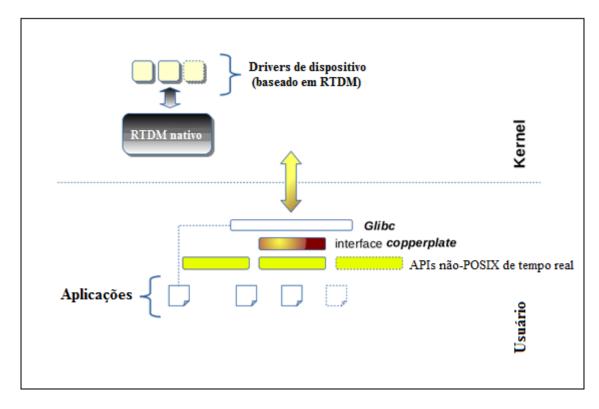

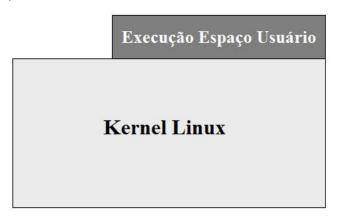

| Figura 5.2 - Modelo de execução espaço de usuário                                                                                                                                                   | 74 |

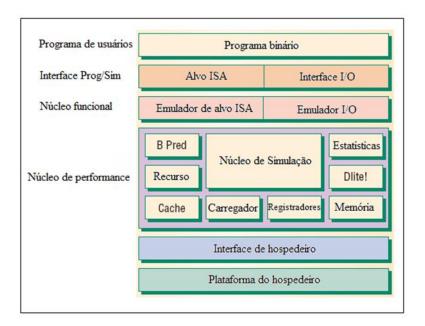

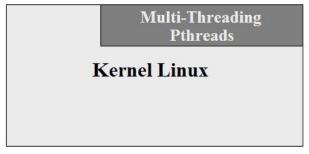

| Figura 5.3 - Modelo de alteração interna do kernel                                                                                                                                                  | 74 |

| Figura 5.4 - Pseudocódigo da chamada XX_ScheduleThread                                                                                                                                              | 75 |

| Figura 5.5 - Pseudocódigo de KS_SuspendTask                                                                                                                                                         | 77 |

| Figura 5.6 - Pseudocódigo de XX_ResumeTask                                                                                                                                                          | 77 |

| Figura 5.7 - Pseudocódigo da chamada XX_ProcessEventSourceTick                                                                                                                                      | 78 |

| Figura 5.8 - Pseudocódigo de escalonador de disparos do Alarme                                                                                                                                      | 80 |

| Figura 5.9 - Pseudocódigo de função KS_TestAlarmW                                                                                                                                                   | 81 |

|                                                                                                                                                                                                     |    |

| Figura 5.10 - Pseudocódigo da chamada KS_PutQueueDataW                              | 82  |

|-------------------------------------------------------------------------------------|-----|

| Figura 5.11 - Pseudocódigo da chamada KS_GetQueueDataW                              | 82  |

| Figura 5.12 - Pseudocódigo do serviço KS_SendMsgW                                   | 84  |

| Figura 5.13 - Pseudocódigo de chamada KS_AckMsg                                     | 84  |

| Figura 5.14 - Pseudocódigo de ReceiveMsgW                                           | 84  |

| Figura 5.15 - Pseudocódigo gerenciador de filas de espera Partição de Memória       | 86  |

| Figura 5.16 - Pseudocódigo do serviço KS_AllocBlkW                                  | 86  |

| Figura 5.17 - Pseudocódigo da função KS_FreeBlk                                     | 87  |

| Figura 6.1 - Pseudocódigo para o benchmark de preempção de tarefa                   | 91  |

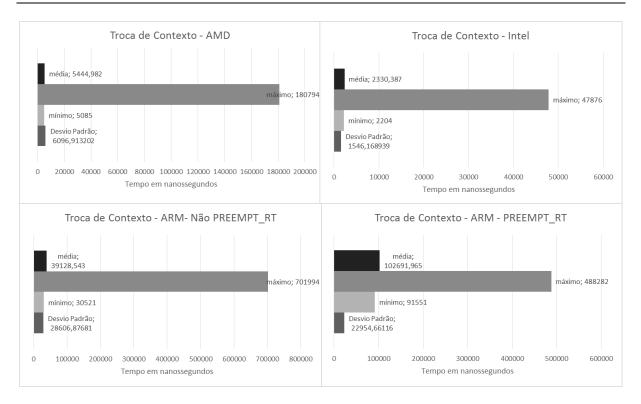

| Figura 6.2 - Resultados para o benchmark de preempção de tarefa                     | 92  |

| Figura 6.3 - Pseudocódigo para o benchmark da participação de memória               | 93  |

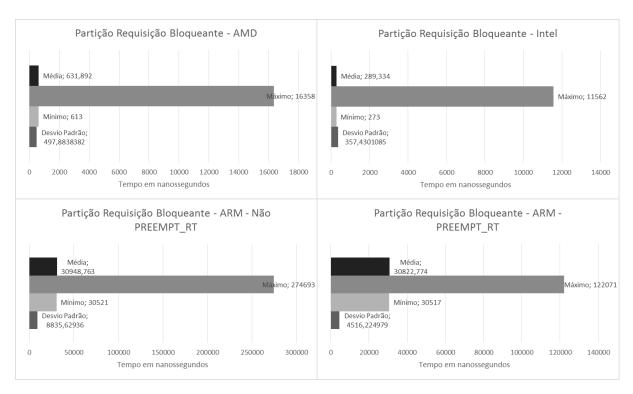

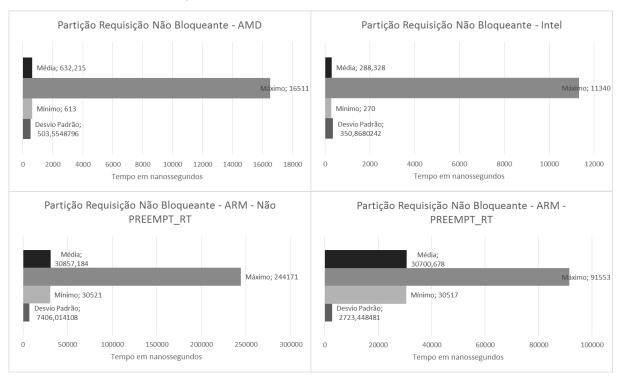

| Figura 6.4 - Gráficos de resultados requisição/devolução bloco de memória Partição. |     |

| Figura 6.5 - Pseudocódigo para o benchmark do mailbox bloqueante                    | 94  |

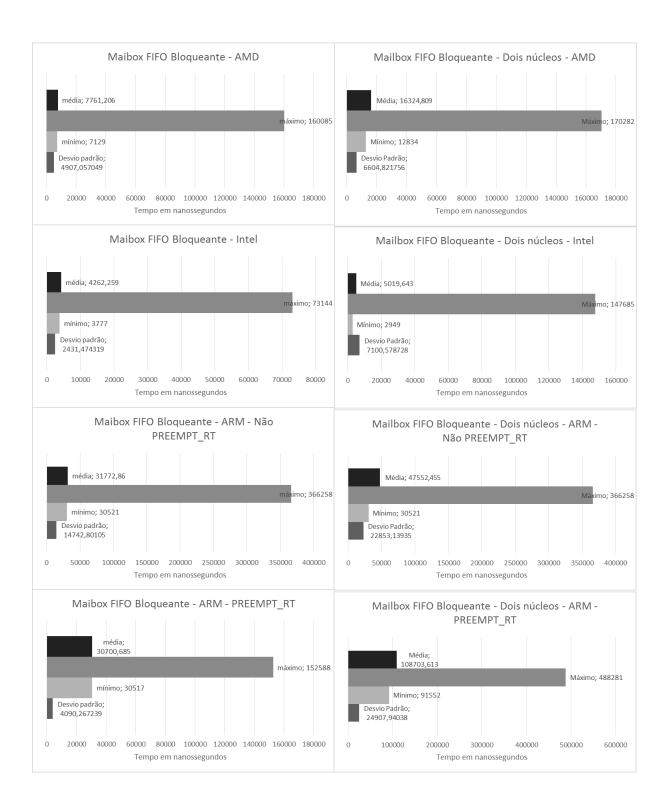

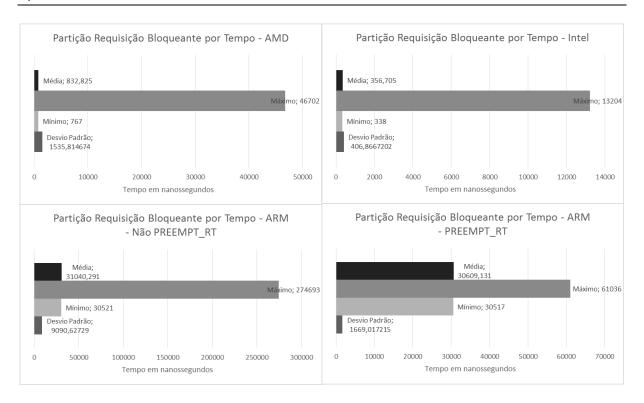

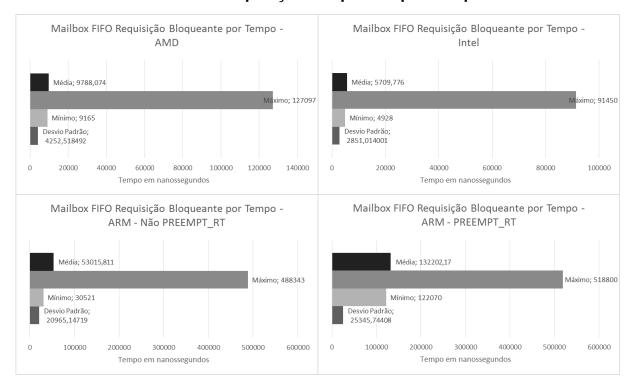

| Figura 6.6 - Resultados para o benchmark de Mailbox bloqueante                      | 96  |

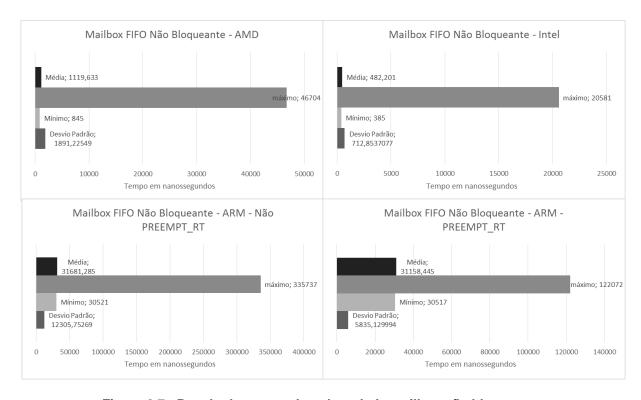

| Figura 6.7 - Resultados para o benchmark de mailbox não bloqueante                  | 97  |

| Figura 6.8 - Pseudocódigo para o benchmark do mailbox não bloqueante                | 97  |

| Figura 6.9 - Pseudocódigo para o benchmark da fila bloqueante                       | 98  |

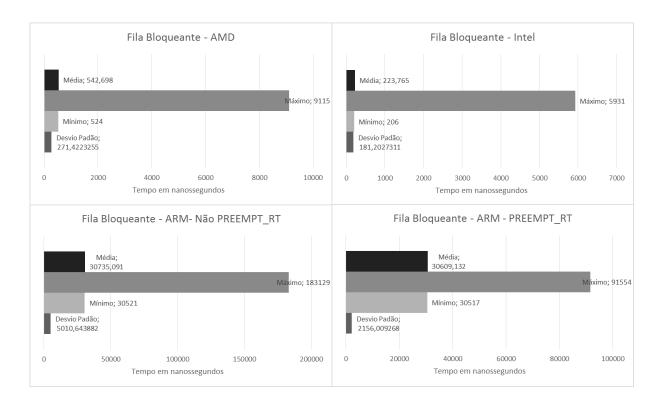

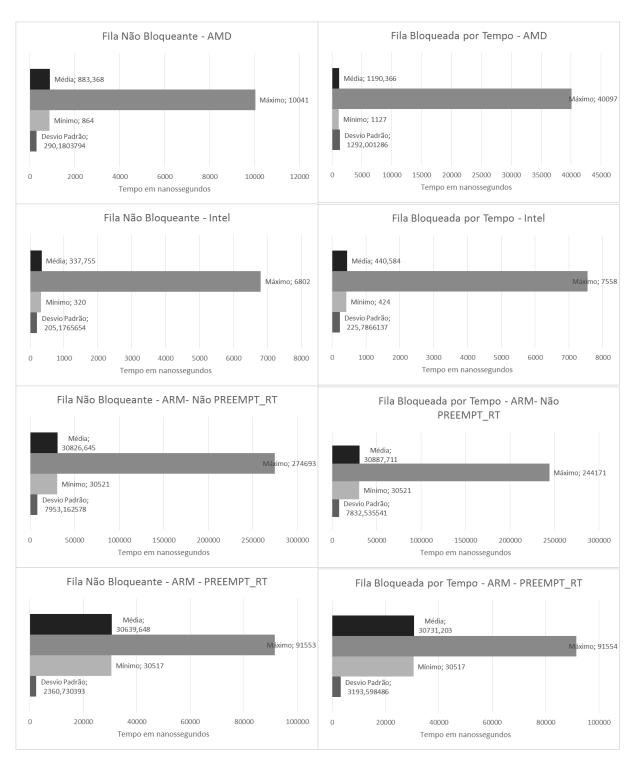

| Figura 6.10 - Resultados para o benchmark da fila                                   | 99  |

| Figura 6.11 - Pseudocódigo para benchmark do alarme                                 | 100 |

| Figura 6.12 - Gráficos do benchmark para disparo de alarme                          | 101 |

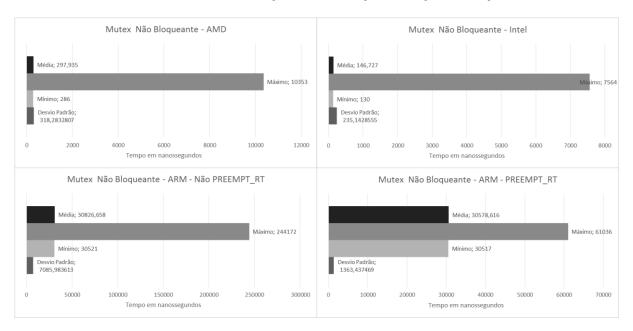

| Figura 6.13 - Pseudocódigo para o benchmark do mutex                                | 101 |

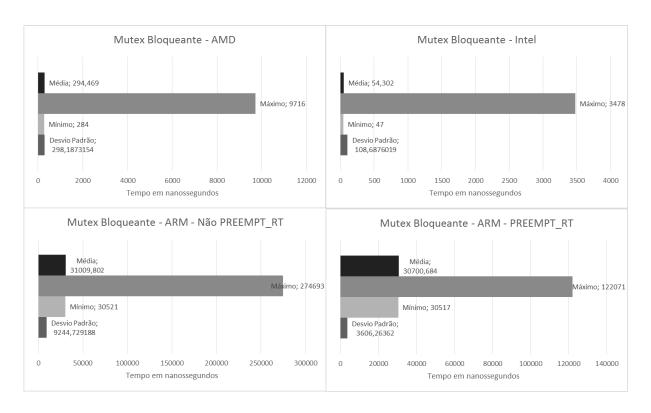

| Figura 6.14 - Gráficos do benchmarch para mutex bloqueante                          | 102 |

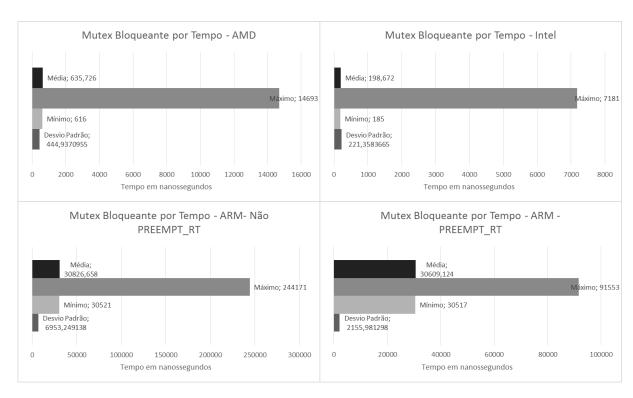

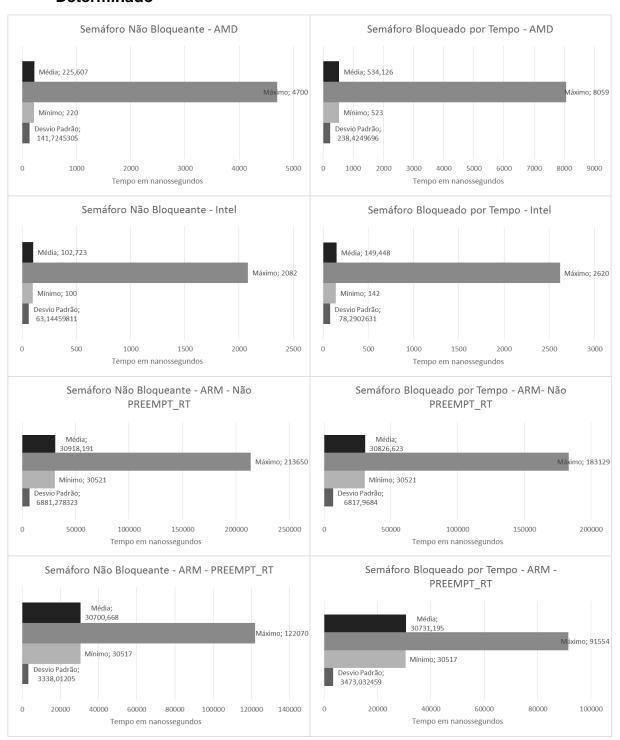

| Figura 6.15 - Pseudocódigo para o benchmark de semáforo                             | 103 |

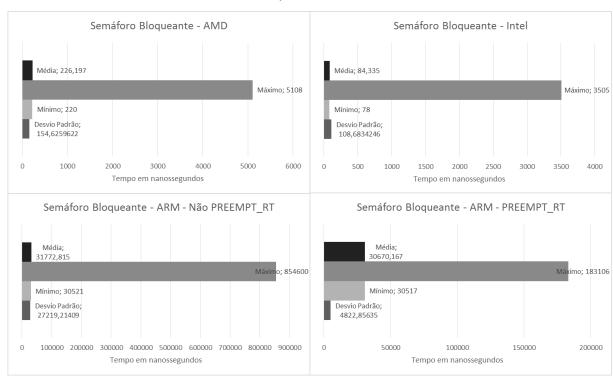

| Figura 6.16 - Resultados para o benchmark de semáforo                               | 103 |

| Figura 6.17 - Mandelbrot obtido no benchmark                                        | 105 |

## LISTA DE TABELAS

| Tabela 2.1 - Comparação entre Sistemas de Tempo Compartilhado e de Tempo Real. [Adaptado de: (LABROSSE et al., 2008)]24 |

|-------------------------------------------------------------------------------------------------------------------------|

| Tabela 5.1 - Outras chamadas do objeto Thread76                                                                         |

| Tabela 5.2 - Outras chamadas para objeto Tarefa77                                                                       |

| Tabela 5.3 - Outras chamadas de <i>Event Source</i> 78                                                                  |

| Tabela 5.4 - Outras chamadas de Contador                                                                                |

| Tabela 5.5 - Outras chamadas objeto Alarme81                                                                            |

| Tabela 5.6 - Outras chamadas do objeto Fila83                                                                           |

| Tabela 5.7 - Outras chamadas do objeto Mensagem85                                                                       |

| Tabela 5.8 - Outras chamadas do objeto Maibox85                                                                         |

| Tabela 5.9 - Outras chamadas do objeto Partição                                                                         |

| Tabela 5.10 - Chamadas referentes ao objeto Exceção87                                                                   |

| Tabela 5.11 - Chamadas referentes ao objeto Mutex                                                                       |

| Tabela 5.12 - Chamadas referentes ao objeto Semáforo89                                                                  |

| Tabela 6.1 - Descrição dos sistemas em que os benchmarks e testes foram realizados                                      |

| 90                                                                                                                      |

| Tabela 6.2 - Coeficiente de variação de preempção de tarefa92                                                           |

| Tabela 6.3 - Coeficiente de variação de requisição/devolução bloco de memória em Partição94                             |

| Tabela 6.4 - Coeficiente de variação para Mailbox bloqueante (Um núcleo)95                                              |

| Tabela 6.5 - Coeficiente de variação para Mailbox bloqueante (Dois núcleos)95                                           |

| Tabela 6.6 - Coeficiente de variação para o benchmark de mailbox não bloqueante.                                        |

| Tabela 6.7 - Coeficiente de variação para o benchmark da fila99                                                         |

| Tabela 6.8 - Coeficiente de variação para benchmark do alarme                                                           |

| Tabela 6.9 - Coeficiente de variação para mutex bloqueante                                                              |

| Tabela 6.10 - Coeficiente de variação para o benchmark de semáforo                                                      |

| Tabela 6.11 - Coeficiente de Variação das medidas do Benchmak104                                                        |

| Tabela 6.12 - Tempo para o teste Mandelbrot                                                                             |

| Tabela 6.13 - Ganho no teste Mandelbrot com duas Tarefas e dois cores106                                                |

## LISTA DE ABREVIATURAS E SIGLAS

ARM - Advanced RISC Machine.

CFS - Completely Fair Scheduler.

**CPU** – Central Processing Unity

**CUDA** – Compute Unified Device Architecture.

FIFO - First in, first out.

**FPGA** – Field-Programmable Gate Array.

**FPU** – Floating-point unit.

**GPU** – Graphics Processing Unit.

IEEE – Institute of Electrical and Electronics Engineers.

**ISO** – International Organization for Standardization.

**ISR** – Interrupt Service Routine.

**IPC** – *Inter-process Communication.*

**HPC** – High Performance Computing.

LIFO - Last in, first out.

**LWP** – Lightweight Processes.

LSB - Least Significant Bit.

MESI - Modified, Exclusive, Shared and Invalid

MOESI – Modified, Owned, Exclusive, Shared and Invalid.

MSB – Most Significant Bit.

**NUMA** – Non-Uniform Memory Access.

**OpenCL** – Open Computing Language.

**PGA** – Partitioned Global Address Space.

**POSIX** – Portable Operating System Interface.

**QPI** – Quick Path Interconnect.

RPC - Remote Procedure Call.

RTOS - Real-Time Operating System.

RTXC - Real-Time Executive in C.

**SMP** – Symmetric Multiprocessor.

SoC - System on Chip.

STR - Sistemas de Tempo Real.

**SPE** – Synergistic Processing Elements.

**SRI** – System Request Interface.

**UMA** – *Uniform Memory Access.*

**VFP** – Vector Floating-Point.

## **S**UMÁRIO

| CAPÍTULO 1 - INTRODUÇÃO                                                     | 13 |

|-----------------------------------------------------------------------------|----|

| 1.1 Taxonomia dos sistemas computacionais                                   | 14 |

| 1.2 Desenvolvimento paralelo                                                | 14 |

| 1.3 Objetivos gerais do trabalho                                            | 16 |

| 1.4 Organização do trabalho                                                 | 17 |

| CAPÍTULO 2 - CONCEITOS BÁSICOS                                              | 18 |

| 2.1 Conceitos básicos                                                       | 18 |

| 2.1.1 Memória compartilhada                                                 | 19 |

| 2.1.1.1 Memória de Acesso Uniforme (UMA -Uniform Memory Access)             | 19 |

| 2.1.1.2 Memória De Acesso Não Uniforme (NUMA - Non-Uniform Memory Access)2  | 20 |

| 2.1.2 Memória distribuída                                                   | 21 |

| 2.2 Sistemas Operacionais De Tempo Real                                     | 22 |

| 2.2.1 Diferenças entre Sistema Operacional de Tempo Real e Sistema de Tempo |    |

| compartilhado2                                                              | 23 |

| 2.3 Arquiteturas Multicores                                                 | 24 |

| 2.3.1 Motivação para Desenvolvimento                                        | 24 |

| 2.3.2 Hardware                                                              | 25 |

| 2.3.2.1 Intel Core Duo                                                      | 25 |

| 2.3.2.2 AMD Dual Core Opteron                                               | 26 |

| 2.3.2.3 Comparação entre Intel e AMD                                        | 28 |

| 2.3.2.4 Arquiteturas de Multiprocessadores Simétricos                       | 28 |

| 2.3.2.5 Arquitetura de chips heterogêneos                                   | 30 |

| 2.3.3 Modelos de Programação Paralela                                       | 32 |

| 2.3.3.1 Modelo de Threads                                                   | 32 |

| 2.3.3.2 Modelo de Passagem de mensagens                                     | 34 |

| 2.3.3.3 Modelo PGAS                                                         | 35 |

| 2.4 Mecanismos de comunicação entre processos                               | 37 |

| 2.4.1 Comunicação cliente servidor                                          | 38 |

| 2.5 Ferramentas para Programação paralela                                   | 39 |

| CAPÍTULO 3 - REVISÃO BIBLIOGRÁFICA                                    | 43 |

|-----------------------------------------------------------------------|----|

| 3.1 Arquiteturas multicore recentes                                   | 43 |

| 3.2 Arquitetura multicore de sistema embarcado recente                | 45 |

| 3.3 Métodos para programação paralela em multicores                   | 46 |

| 3.4 Ferramentas para programação paralela em multicores de tempo real | 48 |

| 3.5 Ferramentas educacionais para programação paralela                | 50 |

| CAPÍTULO 4 - DISCUSSÃO DOS OBJETOS DO KERNEL RTXC                     | 53 |

| 4.1 Responsabilidades de um kernel de tempo real                      | 53 |

| 4.2 Introdução ao kernel RTXC                                         | 53 |

| 4.3 Níveis (Levels)                                                   | 55 |

| 4.4 Objetos executáveis do Kernel RTXC                                | 56 |

| 4.4.1 Exceção (Exception)                                             | 56 |

| 4.4.2 Threads                                                         | 56 |

| 4.4.3 Tarefa ( <i>Task</i> )                                          | 60 |

| 4.5 Semáforo                                                          | 62 |

| 4.6 Mutex                                                             | 63 |

| 4.7 Partição de Memória                                               | 63 |

| 4.8 Fonte de Evento (Event Source)                                    | 64 |

| 4.9 Contador (Counter)                                                | 66 |

| 4.10 Alarm (Alarme)                                                   | 66 |

| 4.11 Fila (Queue)                                                     | 69 |

| 4.12 Mailbox                                                          | 69 |

| 4.13 Mensagem (Message)                                               |    |

| 4.14 Pipe                                                             | 71 |

| CAPÍTULO 5 - IMPLEMENTAÇÃO DA API                                     | 72 |

| 5.1 Considerações iniciais                                            | 72 |

| 5.2 Linux em Tempo Real                                               | 73 |

| 5.2.1 Implementação de kernel extra                                   | 73 |

| 5.2.2 Evitar usar o kernel para requisitos de tempo real              | 74 |

| 5.2.3 Modificar características do kernel do Linux                    | 74 |

| 5.3 Desenvolvimento API                                               | 75 |

| 5.3.1 Thread                                                          | 75 |

| 5.3.2 Tarefa                                                | 76  |

|-------------------------------------------------------------|-----|

| 5.3.3 Fonte de eventos, Contador e Alarme                   | 78  |

| 5.3.4 Fila (Queue)                                          | 82  |

| 5.3.5 Mailbox e Mensagens                                   | 83  |

| 5.3.6 Partição de Memória                                   | 85  |

| 5.3.7 Exceção                                               | 87  |

| 5.3.8 Mutex                                                 | 88  |

| 5.3.9 Semáforo                                              | 88  |

| CAPÍTULO 6 - BENCHMARKS E TESTE NA API-RTXC-LINUX           | 90  |

| 6.1 Introdução benchmark                                    | 90  |

| 6.1.1 Preempção de tarefa                                   | 91  |

| 6.1.2 Requisição/devolução de blocos em partição de memória | 92  |

| 6.1.3 Mailbox                                               | 94  |

| 6.1.4 Fila (Queue)                                          | 98  |

| 6.1.5 Alarme                                                | 99  |

| 6.1.6 Mutex                                                 | 101 |

| 6.1.7 Semáforo                                              | 102 |

| 6.1.8 Resumo dos resultados benchmark                       | 104 |

| 6.2 Testando a API com Mandelbrot Multicore                 | 105 |

| CAPÍTULO 7 - CONCLUSÃO                                      | 107 |

| 7.1 Uso da API-Linux-RTXC                                   | 108 |

| 7.2 Contribuições e Limitações                              | 109 |

| 7.3 Trabalhos Futuros                                       | 110 |

| REFERÊNCIAS                                                 | 111 |

| APÊNDICE A                                                  | 114 |

# Capítulo 1

## INTRODUÇÃO

Buscando uma constate evolução, processadores e a arquitetura de computadores foram aprimorados durante décadas desde seu surgimento e continuam até hoje. No princípio houve uma tendência de se aumentar a frequência de trabalho desses processadores, uma vez que a frequência está diretamente relacionada ao número de instruções executadas num período de tempo.

A abordagem de aumento de *clock* caracterizava em um "ganho fácil de desempenho" para os programadores, uma vez que a melhoria no desempenho dos sistemas computacionais pesava mais para os requisitos de hardware do que com a melhoria de técnicas de programação (LIN; SNYDER, 2009).

No entanto, com relação ao hardware, o aumento de *clock* significa também o aumento de dissipação térmica, ficando evidente para os fabricantes que essa característica se tornaria uma limitação com o passar do tempo. A partir daí, surge a ideia dos computadores multicores, ou seja, em um mesmo chip são condensados dois ou mais núcleos.

A proposição da lei de Moore que prevê a cada dois anos a duplicação do número de transistores, e consequentemente melhorias no processador passaram a ditar a política dos fabricantes de hardware, que puderam adicionar novos recursos e elementos a arquitetura melhorando ainda mais o desempenho dos processadores.

A introdução de computadores multicore possibilitou que outros paradigmas de programação fossem utilizados, pois a utilização desses computadores em aplicações anteriormente escritas de formal serial não representava um ganho de desempenho. Era necessário então surgimento de modelos e ferramentas de programação paralela.

#### 1.1 Taxonomia dos sistemas computacionais

Proposta por Flynn, a classificação de sistemas computacionais engloba as principais organizações de computadores existentes agrupadas em quatro categorias (FLYNN, 1972):

- SISD (Single Instruction, Single Data): Esse tipo de computador é puramente serial, apenas uma instrução é executada por vez e apenas um dado é processado.

O tipo mais simples e mais antigo computador representa essa categoria

- SIMD (Single Instruction, Multiple Data): É um tipo de computador paralelo, em que todas as unidades de processamento executam a mesma instrução em diferentes dados. Essa arquitetura é utilizada em processadores vetoriais e GPUs.

- MISD (*Multiple Instruction, Single Data*): Nesse tipo de computador um único fluxo de dados alimenta diversas unidades de processamento executando diferentes instruções sobre esse mesmo dado. Essa arquitetura embora não usual, é importante para sistemas redundantes e com baixa tolerância a falhas.

- MIMD (Multiple Instruction, Multiple Data): nesse tipo de computador paralelo, diversas instruções são executadas usando diferentes fluxos de dados.

Computadores multicores e sistemas distribuídos são exemplos dessa arquitetura.

#### 1.2 Desenvolvimento paralelo

No paradigma de programação sequencial, um conjunto de instruções é executado de forma serial instrução por instrução. Na programação paralela, diversas operações são executadas simultaneamente.

Com relação à paralelização em nível de hardware pode-se citar: ILP (*Instruction Level Paralallelism*) que é a forma de paralelização no nível de instrução (RAUBER; RUNGER, 2012). Nessa abordagem, uma instrução é subdividida em quatro sub-operações: carregamento, decodificação, execução e escrita. Com essa mudança, não é necessário terminar o processamento de uma instrução para começar

a carregar e executar as sub-operações da próxima instrução, permitindo que mais de uma instrução seja executada simultaneamente. Esse procedimento, conhecido também como *pipelining* de instruções, associado a predições de desvio é responsável pelo aumento no desempenho de um processador.

Outra forma de paralelismo para hardware foi a *Simultaneous Multithreading* (SMT) solução lançada pela Intel também chamada por Hyper-Threading. Nessa tecnologia um núcleo físico executa dois núcleos lógicos, cada processador lógico mantém as suas próprias configurações de arquiteturais de estado, compartilhando apenas os recursos de execução. Essa abordagem permite ganho no desempenho executando mais threads, fazendo poucas modificações no tamanho do desenho do processador (KOUFATY; MARR, 2003).

A programação paralela abriu portas para que se explorasse a capacidade disponibilizada pelos multicores. Porém, sua implementação não é trivial e nem aplicável 100% a todos os contextos.

De acordo com a lei de Amdahl, que calcula o ganho de desempenho em aplicações paralelas, a variável f corresponde à porcentagem do código que precisa ser executado sequencialmente, assumindo valores  $0 \le f \le 1$ , e p número de processadores do computador paralelo. O ganho (*speedup*) máximo é representado pela inequação  $\psi$  (QUINN, 2004):

$$\psi \le \frac{1}{f + (1 - f)/p}$$

Conforme a inequação apresentada, o ganho pode ser igual ou menor que o lado direito da expressão, uma vez que gastos com sincronizações e comunicação entre os componentes não são computados nessa inequação o ganho tende a ser ligeiramente menor.

Como principais modelos de programação paralela em multicores podemos citar: modelo de memória compartilhada, passagem de mensagens e modelo de dados paralelos.

No modelo de memória compartilhada, o paralelismo ocorre através de posições de memória compartilhadas entre os diversos processadores através de um mesmo barramento local que conecta processadores a memória. Diversas tarefas são realizadas simultaneamente tirando proveito dos vários núcleos se comunicando e sincronizando através dessa área compartilhada.

No modelo de passagem de mensagens a organização, paralelização e divisão das tarefas ocorre por meio de trocas de mensagens. Esse modelo favorece a utilização de sistemas distribuídos, embora possa ser utilizado com arquiteturas de memória compartilhada.

No modelo de dados paralelos, também conhecido como PGAS (*Partitioned Global Address Space*), temos um espaço de endereço global. Grupos de tarefas trabalham coletivamente executando uma mesma operação em diferentes áreas de um mesmo arranjo de dados.

#### 1.3 Objetivos gerais do trabalho

As arquiteturas multicores possibilitaram a utilização de tecnologias de processamento paralelo para uso computacional. Ao se programar utilizando o paradigma paralelo é possível obter ganho em desempenho se comparado ao paradigma de programação sequencial.

A complexidade de programação paralela é maior que a programação sequencial, isso se deve preocupações adicionais tais como: sincronização de recursos compartilhados, operações de coerência, existência de regiões críticas e barreiras.

Para sistemas embarcados, que são sistemas de computador construídos dentro de um dispositivo e funcionando como parte do mesmo (BERGER, 2002) existem restrições adicionais. Um sistema embarcado crítico precisa gerar saídas respeitando a intervalos pré-definidos de tempo, podendo ser classificado: "soft" em que falhas correspondem a degradação de desempenho, ou "hard" cujas falhas comprometem o resultado (LABROSSE et al., 2008).

O objetivo deste projeto é prover uma API que permita, aos desenvolvedores que utilizam o tradicional RTOS (*RealTime Operating Systems*), portarem suas aplicações para o ambiente de desenvolvimento baseado no Linux e mostrar através de testes e benchmark o quanto pode ser adequada a API para o contexto que foi idealizada.

#### 1.4 Organização do trabalho

Este trabalho está organizado da seguinte forma:

No capítulo 2 apresentam-se a revisão teórica de conceitos de arquiteturas multicores, paradigmas paralelos, sistemas de tempo real.

No capítulo 3 tem-se a revisão bibliográfica das arquiteturas atuais, ferramentas de programação paralela e educacional.

No capítulo 4 encontra-se a discussão dos objetos do kernel RTXC.

No capítulo 5 são discutidas as estratégias para se tornar o Linux em tempo real, apresentada as chamadas que a API contém e os detalhes de como as principais chamadas foram implementadas.

No capítulo 6 apresentam-se os resultados do benchmark aplicado na API desenvolvida e o teste Mandelbrot Multicore.

No capítulo 7 está a conclusão do trabalho, apresentando-se as contribuições e limitações do trabalho desenvolvido e ideias para trabalhos futuros.

Nos apêndices encontram-se os resultados de benchmark que não foram colocados no capítulo 6.

# Capítulo 2

## **CONCEITOS BÁSICOS**

#### 2.1 Conceitos básicos

No início da computação os programas eram escritos de forma sequencial. Cada instrução era executada uma a uma. Cientistas na busca de se construir máquinas mais velozes, desenvolveram novas tecnologias e processadores que atingiam *clocks* de frequências cada vez mais altas.

O aumento de *clock* tinha relação direta com aumento da vazão, ou seja, como a instrução estava atrelada a ciclos de *clock*, o aumento de ciclos por período significava um aumento de instruções que poderiam ser executadas num determinado período de tempo. Entretanto o aumento na frequência de *clock* também correspondia a um aumento na dissipação térmica. Passado algum tempo o aumento de dissipação térmica se tornou inviável devido à grande dissipação de calor por núcleo.

A crescente demanda por sistemas computacionais mais eficientes abriu a possibilidade de um outro campo, a computação paralela. Desta forma não seria mais o aumento do *clock* o único responsável pelo aumento da vazão e de tarefas executadas, mas o aumento de componentes de processamento (pipelines), núcleos e unidades de processamentos interligadas entre si.

#### 2.1.1 Memória compartilhada

Na memória compartilhada, os núcleos de processamento têm acesso de toda memória através de um espaço de endereço global. Com isso, diversos núcleos podem operar de maneira independente utilizando esses espaços de memória compartilhados. Mudanças nos valores de memória são visíveis a todos os processadores. As máquinas de memória compartilhada têm sido classificadas em (Barney,2015):

#### 2.1.1.1 Memória de Acesso Uniforme (UMA -Uniform Memory Access)

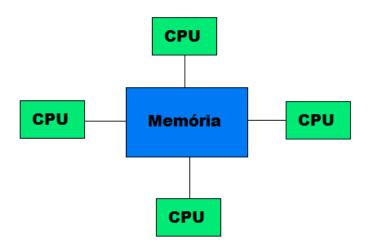

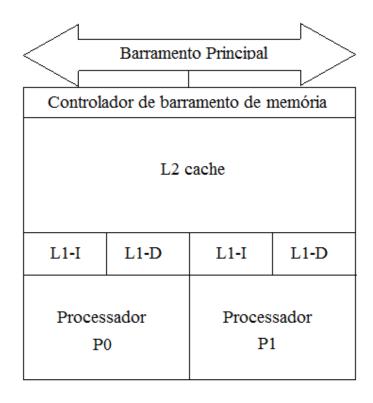

Sendo muito representada nos dias atuais através das SMP (*Symmetric Multiprocessor Machines* – Máquinas de multiprocessador simétrico). Nessas máquinas processadores idênticos tem acesso igual e de mesmo tempo as porções de memória. Algumas vezes chamado de CC-UMA (Cache Coerente UMA), isso significa que atualizações feitas na memória passam a ser conhecidas por todos os processadores. A coerência de cache é realizada em nível de hardware. Na *Figura 2.1* temos a representação da arquitetura UMA.

Figura 2.1 - Representação arquitetura memória de acesso uniforme

## 2.1.1.2 Memória De Acesso Não Uniforme (NUMA - Non-Uniform Memory Access)

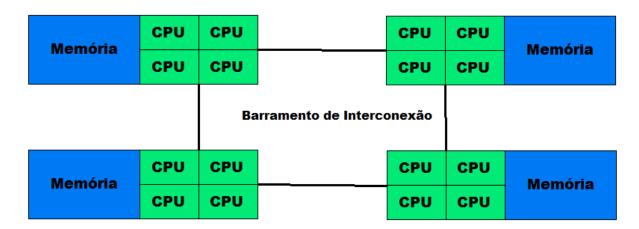

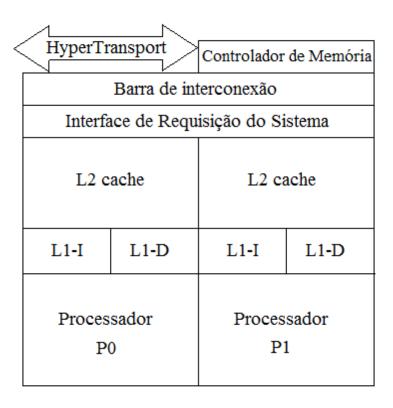

São computadores geralmente construídos pela junção física de duas ou mais SMP. Uma SMP pode acessar diretamente a memória de outra SMP. Nem todos os processadores tem acesso igual e mesmo tempo de acesso a toda a memória. Acesso através do link das memórias é lento. Caso exista coerência de cache é então chamado de CC-NUMA (Cache Coerente NUMA). A Figura 2.2 mostra um exemplo de NUMA:

Figura 2.2 - Representação arquitetura memória de acesso não uniforme.

Como vantagens, a memória compartilhada fornece facilidades na programação graças a perspectiva de acesso global às posições de memória. Podemos citar também a uniformidade e velocidade de troca de mensagens devido à proximidade dos núcleos e memória.

Como desvantagens pode-se destacar a ausência de escalabilidade entre CPU e memória. Adicionando mais núcleos aumenta-se geometricamente o tráfego de informação no barramento memoria-CPU, além de se aumentar a complexidade no gerenciamento da coerência de caches. Outra desvantagem é que o programador além de ser responsável pela sincronização é também responsável pelo acesso correto à memória global.

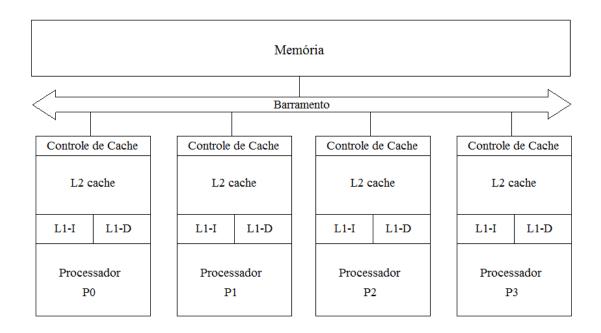

#### 2.1.2 Memória distribuída

A tecnologia envolvida na construção de sistemas de memória distribuída pode variar bastante. Porém uma coisa é comum: o acesso de memórias distribuídas é intermediado por uma rede que conecta as memórias entre processadores. O mapeamento das memorias não é global, como no caso da memória compartilhada. Portanto, como o mapeamento passa a ser local não existe a necessidade de se verificar a coerência de cache. Por outro lado, em geral, a sincronização e comunicação devem ser explicitamente definidas pelo programador. A construção da rede de comunicação pode variar sendo desde a redes de altíssimo desempenho a redes comuns como a Ethernet. Na Figura 2.3 temos um esquema de memória distribuída:

Figura 2.3 - Representação da arquitetura de memória distribuída.

#### Como vantagens podemos citar:

- A memória é escalável com o número de processadores, ou seja, o aumento do número de processadores também aumenta o tamanho de memória proporcionalmente.

- Cada processador pode acessar rapidamente sua própria memória, sem congestionamento ou atrasos ocorridos pelas políticas de coerência em caches globais.

- Eficiência nos custos, pois é possível utilizar os produtos e redes que já estão disponíveis a venda no mercado.

#### Como desvantagens:

O programador se torna responsável por detalhes associados à comunicação de dados entre processos. Pode ser difícil de se mapear estruturas baseadas em memoria global, usando este arranjo.  Temos também o tempo de acesso não uniforme a dados, por exemplo, dados em nós distantes tem um tempo de acesso muito grande em relação aos nós locais.

#### 2.2 Sistemas Operacionais De Tempo Real

Segundo (SILBERSCHATZ et al., 2013) o sistema operacional é um programa que gerencia o hardware de um computador. É também responsável por providenciar a base para os programas de computador além de agir como um intermediário entre o usuário do computador e o hardware do computador. Cada sistema operacional pode ser desenhado para atender um determinado objetivo, por exemplo sistema operacional em mainframes é feito para tirar o máximo de proveito da utilização do hardware. Já os PC, computadores pessoais, para jogos complexos, aplicações comercias e outras atividades gerais.

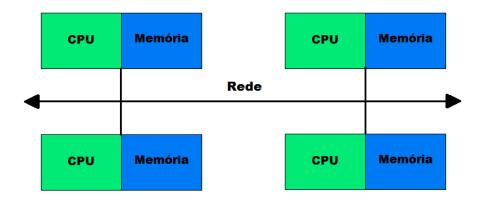

Para os sistemas de tempo real (STR), tem-se outra variável importante a se considerar: o tempo decorrido a partir do momento que o sistema recebe o estímulo, até o tempo em que a saída é gerada. Portanto, além de se gerenciar os recursos de hardware e intermediar a interação com o usuário, o sistema deve escalonar as tarefas críticas de forma a gerar saídas respeitando a tempos pré-determinados. Geralmente sistemas de tempo real mantém uma interação continua com o ambiente. Conforme Figura 2.4:

Figura 2.4 - O STR reage a entrada do ambiente produzindo uma saída que afeta o ambiente[Adaptada de (LABROSSE et al., 2008)]

Além de gerar saídas corretas um STR deve se ater às restrições de tempo ou sofrer consequências significativas para o sistema. Quando essas consequências consistem em degradação do desempenho sistema, mas não em uma falha, o sistema é classificado como sistema de tempo real "soft". Já no caso de as consequências serem uma falha o sistema é classificado como sistema de tempo real "hard" (por exemplo o freio ABS em um automóvel).

Uma função de sistema (hardware, software ou combinação de ambos) é considerada uma função de tempo real "hard", se e somente se o tempo limite precisa ser sempre atendido, caso contrário a tarefa falha. Um sistema pode ter uma ou mais tarefas de tempo real hard, assim como outras tarefas que não são de tempo real. Isso é aceitável, desde que o sistema agende propriamente as tarefas atendendo sempre o tempo limite das funções de tempo real "hard" (LABROSSE et al., 2008).

# 2.2.1 Diferenças entre Sistema Operacional de Tempo Real e Sistema de Tempo compartilhado

Sistemas de tempo real diferem de sistemas de tempo compartilhado em três áreas fundamentais:

- Alto grau de escalonabilidade requerimentos de tempo do sistema precisam ser satisfeitos a elevados graus de uso de recursos.

- Pior caso de latência assegurar-se que o sistema ainda irá funcionar mesmo no pior caso de resposta a eventos.

- Estabilidade sob sobrecarga transitória Quando o sistema é sobrecarregado por eventos e se torna impossível atingir todos os tempos limites, o tempo limite das tarefas críticas precisa ser garantido.

Na Tabela 2.1 temos a comparação de sistemas de tempo compartilhado *versus* sistemas de tempo real.

Tabela 2.1 - Comparação entre Sistemas de Tempo Compartilhado e de Tempo Real. [Adaptado de: (LABROSSE et al., 2008)].

| Característica        | Sistema de Tempo Compartilhado | Sistemas de Tempo Real                |

|-----------------------|--------------------------------|---------------------------------------|

|                       | Alta vazão                     | Escalonabilidade e capacidade das     |

| Capacidade do sistema |                                | tarefas do sistema cumprirem seu      |

|                       |                                | tempo limite                          |

|                       |                                | pior caso de latencia assegurado, que |

| Responsividade        | tempo médio de resposta rápido | é o pior caso de tempo de respota a   |

|                       |                                | eventos                               |

|                       | divisão justa                  | Estabilidade - quando o sistema é     |

| Sobragarga            |                                | sobrecarregado, tarefas importantes   |

| Sobrecarga            |                                | tem seu prazo contemplado enquanto    |

|                       |                                | outras são adiadas                    |

#### 2.3 Arquiteturas Multicores

#### 2.3.1 Motivação para Desenvolvimento

Com a aperfeiçoamento da tecnologia de fabricação de processadores, aproveitando-se da tendência predita pela lei de Moore, os fabricantes passaram a agregar mais de uma unidade de processamento a um único chip. Como essa unidade de processamento representa a estrutura de um processador típico passou a ser denominada de *core* ou núcleo.

Com o advento dos processadores multicores, entre 2005 e 2006 novas questões surgem nas comunidades de desenvolvedores (LIN; SNYDER, 2009):

- Durante muito tempo a melhoria de desempenho baseava-se exclusivamente na melhoria do hardware fazendo com que as técnicas de desenvolvimento de software paralelo pouco evoluíssem;

- Os programas existentes até então não podiam tirar proveito dos multicores diretamente;

- Programas que não exploram os chips multi-core, não experimentam nenhuma melhoria no desempenho;

- Muitos programadores da época não sabiam como escrever programas paralelos.

Isso despertou a necessidade de mudança da comunidade e busca por desenvolvimento de novas técnicas, bibliotecas e suporte em linguagens para a escrita de programas paralelos e reescrita de programas existentes.

#### 2.3.2 Hardware

A IBM em 2002 foi a primeira fabricante a anunciar um processador multicore com o PowerPC 970, em maio de 2005 a AMD introduz o Dual Core Opteron e a Intel apresenta o Core Duo Pentium em janeiro de 2006.

#### 2.3.2.1 Intel Core Duo

As seguintes características são encontradas no processador Intel Core Duo:

- 2 processadores de 32 bits em um chip;

- Cada processador tem seu próprio 32K L1 cache de instrução e memória;

- 2MB ou 4MB de L2;

- Comunicação rápida entre dois processadores através de memória compartilhada;

- Controlador de memória, controlador entrada e saída.

- Comunicação rápida entre processadores através de memória compartilhada.

O projeto do Intel Core Duo é baseado na arquitetura do Pentium M, portanto um programa com um thread irá executar como velocidade comparável ao processador Pentium M. Em termos de codificação, existe consistência de dados entre os núcleos quando uma posição da memória é acessada. Isso ocorre porque quando o controlador de barramento faz uma requisição na memória, o dado é copiado para o cache L2, cache este compartilhado em ambos os núcleos. Após isso, ocorre a transferência para o cache L1 do processador que trabalhará com a instrução. Na *Figura 2.5* temos a estrutura lógica do processador Intel Core Duo o lado frontal do barramento faz a conexão com a memória RAM.

Figura 2.5 - Organização lógica do Intel Core Duo. [Adaptado de:(LIN; SNYDER, 2009)]

Uma possível complicação ocorreria quando os dois núcleos tentam alterar o valor numa mesma posição de memória, gerando inconsistências nos dados. Nesse caso, entra em ação o protocolo MESI (*Modified, Exclusive, Shared and Invalid* – Modificado, Exclusivo, Compartilhado e Invalido) que através desses quatro estados gerencia o conflito entre os threads. Embora o protocolo resolva os problemas de coerência permitindo com que o uso dos threads ocorre convenientemente, é acrescentado um atraso por conta da verificação do protocolo e a duplicação do consumo da banda do acesso à memória. Para contornar essa situação a Intel dobrou a média de banda disponível no Core Duo (LIN; SNYDER, 2009).

#### 2.3.2.2 AMD Dual Core Opteron

As seguintes características são encontradas no processador AMD Dual Core Opteron:

- Dois processadores AMD 64 bits num único chip;

- Cada processador possui 64k L1 de cache para dados e instruções;

- 1MB de L2 Cache separados para cada núcleo;

- Arquitetura de conexão direta para acesso de memória compartilhada;

- Comunicação rápida no próprio chip entre os dois núcleos através da Interface de Requisição do Sistema.

O Sistema de Interface de Requisição do Sistema (SRI) é responsável pela coerência da memória, fazendo com que o sistema veja uma única imagem. O protocolo usado é MOESI, que assemelha ao MESI adicionando o estado *owned* (pertencido). Esse estado permite os valores de cache sejam compartilhados entre processadores, mesmo quando os dados da memória RAM estão desatualizados. Os acessos a memória RAM são realizados através do padrão da indústria HyperTransport technology. Na *Figura 2.6* temos a representação do processador AMD.

Figura 2.6 - Organização lógica do AMD Dual Core Opteron.[Adaptado de: (LIN; SNYDER, 2009)]

#### 2.3.2.3 Comparação entre Intel e AMD

A principal diferença entres os processadores está no cache L2. O processador AMD é um processador privado, enquanto o Intel é compartilhado. O fato da coerência SRI atrás de L2, permite maior memória privada e facilidade de que a coerência seja combinada entre outros processadores (essa característica é da arquitetura conhecida como multiprocessador simétrico).

A característica do processador Intel de ser compartilhado, faz com que tenha baixa latência na comunicação interna do chip. Por isso, nessas arquiteturas apresentadas, um sistema que tenha apenas um processador (de dois núcleos) será mais conveniente a arquitetura da Intel, já um sistema que tenha mais de um processador (de dois núcleos cada) a arquitetura AMD será a mais adequada. Na perspectiva do programador essas diferenças são praticamente imperceptíveis, sendo vistas apenas como implementação em memória compartilhada.

#### 2.3.2.4 Arquiteturas de Multiprocessadores Simétricos

Segundo (LIN; SNYDER, 2009) os chamados Multiprocessadores Simétricos (SMP) são computadores paralelos que acessam uma única memória lógica sendo esta porção de memória localizada fisicamente próxima ao processador. Para se ter uma visão consistente da memória, existe um ponto de conexão comum a todos processadores: o barramento de memória. Nesse barramento, cada processador pode verificar a atividade na posição de memória abaixo na *Figura 2.7* tem-se a representação logica do SMP.

Os controladores de cache sempre verificam através do barramento de memória, se o endereço está referenciado por outros processadores e ajustando o marcador de controle nos seus valores de cache, para assegurar a coerência do uso do cache.

Figura 2.7 - Diagrama lógico de Multiprocessadores Simétricos. [Adaptada de: (LIN; SNYDER, 2009)]

O processador P1 pode fazer, por exemplo, a requisição ao bloco y na memória e supondo que o processador P2 já tenha esse bloco em cache, quando o P2 verifica o barramento fica ciente da requisição e assinala o marcador de controle como "compartilhado". Se o processador P3 faz a requisição para escrever no bloco y, então tanto o P1 e P2 veem essa requisição e invalidam sua própria cópia, deixando que apenas o P3 tenha acesso. No momento em que P3 finalizar a escrita, a memória será atualizada e refletirá as requisições ao bloco y com o novo valor.

O procedimento de verificação no barramento garante a coerência, porém se torna um ponto de limitação uma vez que todos os processadores concorrem para utilização desse meio. Por essa razão computadores SMP geralmente tem menos que 20 conexões no barramento de memória (LIN; SNYDER, 2009).

As máquinas SMP atingem seu melhor desempenho em duas situações:

• Quando são pequenas e agrupadas próximas do barramento de memória;

Quando tem um protocolo de cache eficiente, reduzindo assim as requisições ao barramento diminuindo o congestionamento do mesmo.

#### 2.3.2.5 Arquitetura de chips heterogêneos

Diferente da arquitetura SMP que replicava processadores idênticos, na arquitetura heterogênea existe a possibilidade de agregar processadores adjuntos (attached processors) que podem executar tarefas mais especializadas. Nessa estrutura o processador padrão executa as instruções gerais difíceis de se paralelizar enquanto o processador adjunto executa a parte intensiva computacional. Alguns exemplos que seguem esse padrão:

- Unidades de Processamento Gráfico (GPU);

- FPGAs (*Field Programmable Gate Array* Arranjo de Portas Programável em Campo);

- Processador Cell usado em vídeo games.

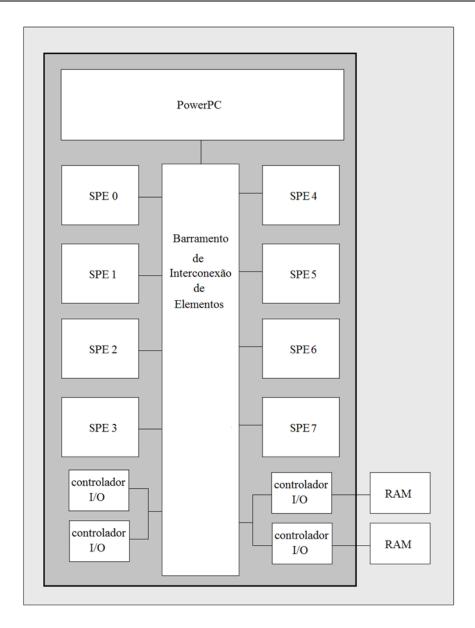

O processador Cell desenvolvido em conjunto pela Sony, IBM e Toshiba. Tem a seguinte estrutura:

- Processador PowerPC 64 bits e dual-theaded;

- Oito SPE (Synergistic Processing Elements Elementos de processamento sinérgico) capaz de executar instruções vetoriais;

- Cada SPE tem 256KB no chip de RAM;

- Alta velocidade no Barramento de Interconexão de Elementos conectando os SPEs.

O processador Cell não providencia a coerência de memória para os SPEs, nessa arquitetura foi escolhida simplicidade e desempenho ao invés de conveniência ao se programar. Na *Figura 2.8* temos o esquema do processador Cell.

Figura 2.8 - Arquitetura processador Cell

O processador PowerPC é o núcleo da linha de múltipla execução sendo responsável também pelo controle dos SPEs. O SPE é um processador RISC com organização SIMD de 128 bits (KAHLE et al., 2005).

A complicação nessa arquitetura é gerenciar corretamente os dados até os SPEs e manter todos funcionando, quando atingido esse objetivo os processadores Cell produzem vazões surpreendentes.

#### 2.3.3 Modelos de Programação Paralela

#### 2.3.3.1 Modelo de Threads

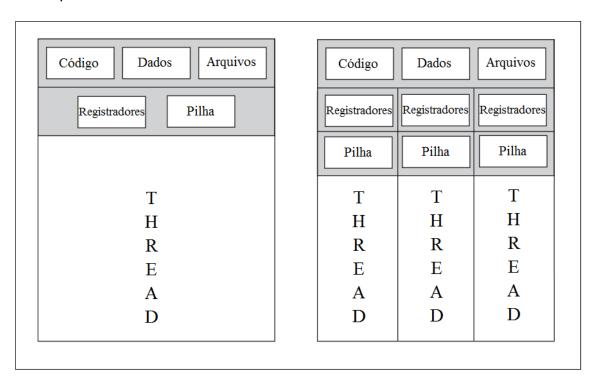

O thread é a menor unidade de utilização de um processador, cada thread é formado por número de identificação ID de thread, contador de programa e sua própria pilha. Ela também compartilha com outros threads recursos do processo a que pertence como: seção de código, dados, recursos do sistema operacional (SILBERSCHATZ et al., 2013). Na *Figura 2.9* é apresentado o processo com um thread e processo *multithreaded*.

Figura 2.9 - À esquerda um processo com um thread e a direita um processo multithreaded.

A utilização de threads beneficia o sistema computacional com:

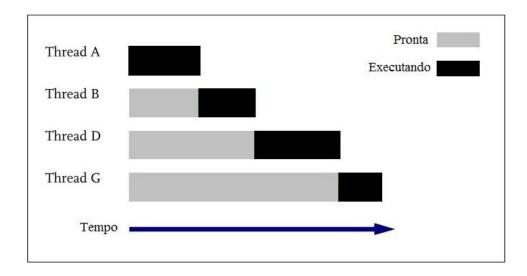

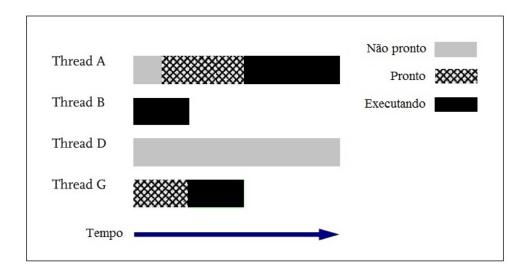

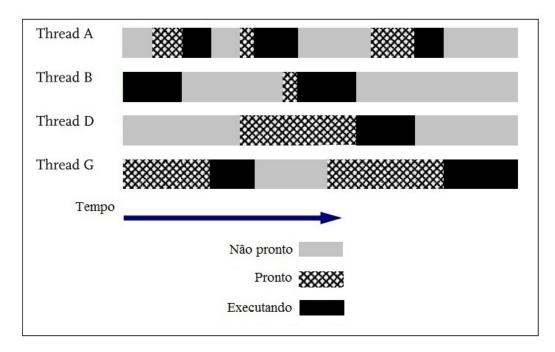

- Responsividade: as tarefas do processo são divididas em sub-rotinas e cada sub-rotina é executada em um thread diferente. Com isso, caso um thread demore para responder ou esteja bloqueado, as demais sub-rotinas continuam funcionando normalmente, pois os threads trabalham independentemente entre si.

- <u>Partilhamento de recursos</u>: os threads compartilham diretamente recursos do processo;

- <u>Economia</u>: é mais custoso criar processos do que novas threads, isso se deve ao compartilhamento de recursos. Como consequência da diferença de tamanho, a troca de contexto nos próprios threads é muito mais rápida também;

- <u>Escalabilidade</u>: em um sistema *multithread* é possível alocar um thread para cada processador disponível, tirando grande proveito da arquitetura *multicore*.

O esforço dos fabricantes para uma padronização gerou duas principais implementações: POSIX Treads e OpenMP.

#### 2.3.3.1.1 POSIX Treads

POSIX thread (*Portable Operating System Interface thread*), conhecido também como Pthreads, surgiu como padrão em 1995 especificado pela *IEEE POSIX* 1003.1c standard.

Os Pthreads são implementados na linguagem C através do arquivo *header* ou biblioteca (Pthread.h). Essa biblioteca oferece suporte para criação e destruição de threads, além de algumas outras funções de coordenação de threads como: *locks*, *mutex*, seções críticas, semáforos e variáveis condicionais.

Nesse modelo de programação a memória *heap* é alocada dinamicamente e compartilhada entre os demais threads. Os programadores devem gerenciar corretamente o uso de dados compartilhado de forma a evitar *deadlocks* e condições de corridas (CHOUGULE; GUTTE, 2014).

#### 2.3.3.1.2 OpenMP

OpenMP (*Open Multi-Processing*) é padronizada pelo consórcio OpenMP Architecture Review Board dos quais participam as empresas como AMD, IBM, Intel, Cray, Fujitsu, Nvidia, Red Hat, Texas Instruments, Oracle e outras.

OpenMP é uma API que suporta a plataforma de memória compartilhada, multiprocessamento nas linguagens C, C++ e Fortran. Diferente de Pthreads que é estruturada através de bibliotecas, OpenMP fornece um conjunto de diretivas de compilação, "pragmas" que orientam o gerenciamento das threads e biblioteca de rotinas. As principais vantagens são a escalabilidade e alta portabilidade, podendo suportar desde computadores pessoais até a supercomputadores.

Nessa padronização o gerenciamento dos threads é feito de maneira implícita. Um thread "mestre" é responsável por dividir as tarefas para um número específico de threads "escravos", esses threads rodam de forma concorrente podendo ser alocados em diferentes processadores. Terminado as tarefas os threads são juntados novamente em um só (thread mestre). É possível determinar quantos processadores, número de threads, mapeamento de seções críticas, sincronizações entre outras, através de diretivas de compilação ou parâmetros, ou funções. (T.C et al., 2011).

#### 2.3.3.2 Modelo de Passagem de mensagens

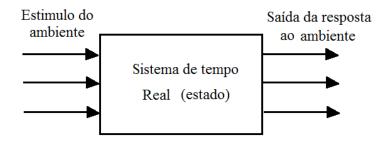

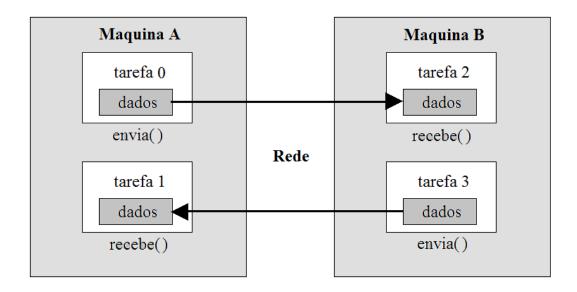

Esse modelo de programação paralela consiste na troca de mensagens entre tarefas que podem estar na mesma máquina, ou em diferentes máquinas, sendo utilizado principalmente para arquitetura de memória distribuída.

As funções envia() e recebe() controlam o fluxo de comunicação, a passagem de mensagem é bidirecional e as tarefas envolvidos precisam colaborar para a transferência de dados. Na *Figura 2.10* o esquema das atividades de comunicação é esquematizado.

Figura 2.10 - Esquema do modelo de passagem de mensagens

Com relação à estrutura das memórias existem dois tipos de abordagem e são usadas duas formas de movimentação: referências a memória no caso do uso de memórias locais, e passagem de mensagens no caso de acesso não local de memória. Devido as chamadas padronizadas e bem definidas, esse padrão é

considerado mais fácil de se depurar do que os padrões de memória compartilhada (LIN; SNYDER, 2009).

#### 2.3.3.2.1 Inteface de Passagem de mensagens (MPI)

O MPI (*Message Passing Interface*) é um padrão de bibliotecas baseado no consenso de fabricantes, pesquisadores, desenvolvedores de software e usuários. Embora, não seja um IEEE ou ISSO, é considerado um padrão da indústria para escrita de aplicações HPC (*High Performance Computing*).

MPI fornece portabilidade, eficiência, padronização e funcionalidades, sendo possível passar mensagens ponto a ponto, como também mensagens globais. Além disso, fornece padrão para bibliotecas de escrita, depuração e teste de desempenho. As implementações estão disponíveis nas linguagens C, C++ e Fortran e suas distribuições mais conhecidas são: GridMPI, LAM/MPI, OpenMPI, MPICH e MVAPICH.

A divisão das tarefas ocorre de maneira análoga ao modelo Pthreads. Apesar, do gerenciamento implícito de threads, cabe ao programador mapear quais tarefas serão executadas e por quais processos. A comunicação usa o modelo de trocas de mensagens entre processos descritos no item 2.3.3.2 de passagem de mensagens.

A vantagem para o usuário é que MPI é padronizado em vários níveis, por isso pode-se utilizar a mesma sintaxe não importando a implementação. Cada chamada MPI deve comportar-se de maneira semelhante independente da implementação, garantindo a portabilidade de aplicações paralelas. (YANG et al., 2009).

Devido a sua característica geral, MPI favorece a sua utilização em sistemas distribuídos, apesar de ser possível também utilizá-lo em sistemas de memória compartilhada (porém com degradação no desempenho em relação ao modelo de memória compartilhado).

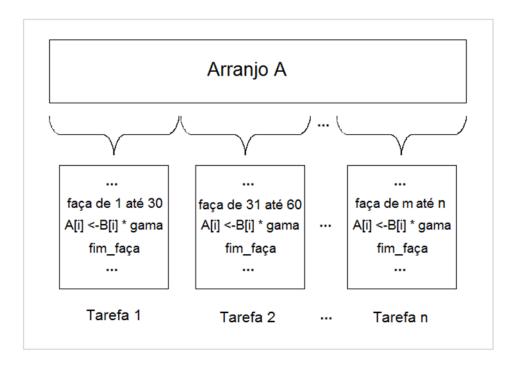

#### 2.3.3.3 Modelo PGAS

O PGAS (Partitioned Global Address Space- Espaço de endereço Global Particionado) é um modelo de programação paralelo que visa melhorar a

produtividade na programação e aumentar o desempenho da aplicação. A principal ideia desse modelo é que o compartilhamento de endereço global favorece a produtividade, porém é necessário que se faça diferenciação entre acessos a dados locais e remotos de forma a se realizar otimizações de desempenho e suporte a escalabilidade em arquiteturas paralelas de larga escala (WAEL et al., 2015).

Como principiais características, esse modelo de dados paralelo possui (Barney, 2015):

- Espaço de endereço global;

- A maior parte do trabalho paralelo é feita buscando desempenho em operações de conjunto de dados, como arranjos ou cubo;

- Um conjunto de tarefas trabalha coletivamente em uma mesma estrutura de dados, entretanto cada tarefa trabalha em uma porção diferente dessa mesma estrutura;

- Tarefas executam a mesma operação em sua partição. Na Figura 2.11 temos um esquema que representa o modelo PGA.

Figura 2.11 - Esquema de operação PGAS - [Adaptado de: (BARNEY, 2015)]

Na década de 1990 surgem as implementações de PGA: Co-Array como extensão de Fortram, Titanium extensão de Java e Unified Parallel C para a linguagem C.

Por volta da década de 2000 surgem três novas linguagens: Chapel, X10 e Fortress. Essas linguagens aparecem devido ao projeto HPCS (High Productivity Computing Systems gerenciado pelo DARPA (*Defense Advanced Research Projects Agency*- dos Estados Unidos), tendo como foco agregar em relação as linguagens anteriores: o aumento na produtividade, facilidade de programação, alto desempenho, portabilidade.

Entretanto, apesar do entusiasmo promovido pela criação dessas linguagens elas acabaram não se difundindo. Isso se deu ao seu nicho específico de aplicações (por exemplo, as aplicações que usam arranjos globais), ou de não provarem um maior impacto em sua utilização.

#### 2.4 Mecanismos de comunicação entre processos

Um programa de computador enquanto permanece em seu dispositivo de armazenamento é uma entidade passiva. No entanto, quando é carregado para a memória passa a ser um elemento ativo de execução tornando-se um processo.

Os processos possuem um contador de instruções que aponta para próxima instrução a ser executada. Têm sua própria pilha que contém informações temporárias, sobre variáveis e parâmetros. A seção de dados contém as variáveis globais, além disso os processos têm uma porção do *heap* que é alocada em tempo de execução.

Um processo pode ser classificado como independente ou colaborativo. No processo independente nenhum outro processo afeta ou é afetado pelo mesmo. Já no processo colaborativo o mesmo pode afetar ou ser afetado por outro processo executado no sistema (SILBERSCHATZ et al., 2013).

O termo IPC (Interprocess Communication), refere-se aos mecanismos utilizados para comunicação entre processos. As duas principais estratégias de

comunicação entre processos são: o compartilhamento de memória e a troca de mensagens.

No paradigma de memória compartilhada, uma região de memória é explicitamente definida como compartilhada entre os processos. Essa região de memória compartilhada deve ser cuidadosamente gerenciada, a fim de se evitar inconsistência de dados. Além desse gerenciamento, operações do tipo "produtor-consumidor" devem ser sincronizadas corretamente de forma a se evitar o consumo de produtos inexistentes.

De uma forma geral, o modelo de memória compartilhada é mais rápido que o modelo de troca de mensagens, isso ocorre devido a uma necessidade menor de chamadas do sistema. Além disso, uma vez estabelecida a área compartilhada os próprios processos passam a gerenciar, não necessitando mais intervenção do *kernel* do sistema operacional (SILBERSCHATZ et al., 2013)

No modelo de troca de mensagens é possível se realizar comunicação entre processos mesmo no caso em que não compartilham endereços de memória. Esse tipo de comunicação se torna especialmente útil em sistemas distribuídos, uma vez que os processos não necessitam estar na mesma máquina para se comunicar.

No paradigma de troca de mensagens é possível que se envie mensagens de tamanho fixo ou variável. Uma ligação de comunicação deve existir entre os processos, que pode ser memória compartilhada, barramento de hardware ou rede. A comunicação pode ser realizada diretamente, nesse caso deve-se nomear o remetente ou/e destinatário. Para a comunicação indireta são usadas caixas de mensagens ou portas. A mensagem pode ser bloqueante ou não bloqueante, conhecida como síncrona ou assíncrona, respectivamente.

#### 2.4.1 Comunicação cliente servidor

Para a estrutura cliente-servidor de IPC pode-se destacar como principais estratégias (SILBERSCHATZ et al., 2013)

Sockets: nessa abordagem uma conexão é feita a concatenação de um endereço IP e um número de porta. A conexão é feita ponto-a-ponto usando protocolo TCP ou UDP através de uma rede.

- RPC (Remote Procedure call): é uma abstração de chamadas de procedimentos para sistemas conectados por rede. Nessa abordagem, um procedimento remoto é iniciado pelo cliente, enviando uma mensagem para um servidor remoto com o procedimento a ser executado. O comando é executado no servidor e a resposta é enviada ao cliente.

- Pipe: Um dos primeiros mecanismos de IPC a ser implementado em sistemas UNIX. Sendo um dos mecanismos mais simples de comunicação entre processos. Existem duas variantes, ambas sendo usadas para a comunicação em uma mesma máquina:

- O Pipe comum: o produtor escreve no fim do pipe, e o consumidor começa a ler a partir da outra extremidade. A comunicação é unidirecional, sendo necessário dois pipes para a comunicação nas duas direções. Sua existência está atrelada à comunicação entre dois processos. Sendo assim, tão logo termine a comunicação o pipe deixa de existir;

- O Pipe nomeado: nesse tipo de pipe a comunicação pode ocorrer de forma bidirecional, embora possa se utilizar uma direção de cada vez (halfduplex). Uma vez estabelecido o pipe nomeado pode ser utilizado na comunicação de diversos processos e continua existindo mesmo que a comunicação entre determinados processos termine.

#### 2.5 Ferramentas para Programação paralela

À medida que os processadores deixaram de buscar um aumento do *clock* como principal fator de desempenho e buscaram melhorar a sua própria estrutura interna, aumentando o número de núcleos, melhorando capacidade de instruções vetoriais, tornou-se importante o desenvolvimento de ferramentas que auxiliassem na produção de software que aproveitasse esse novo potencial.

Tarefas que antes eram simples de serem implementadas em código sequencial se tornaram mais complexas no contexto paralelo. Necessidades adicionais surgiram como sincronizações, controles de regiões críticas, vazamento de memória, entre outros. Entre as ferramentas que se destacaram por possuir interface visual, diversos recursos para gerenciar características do contexto paralelo e facilidade de uso podemos citar: TotalView, Allinea DDT e Intel Parallel Studio XE.

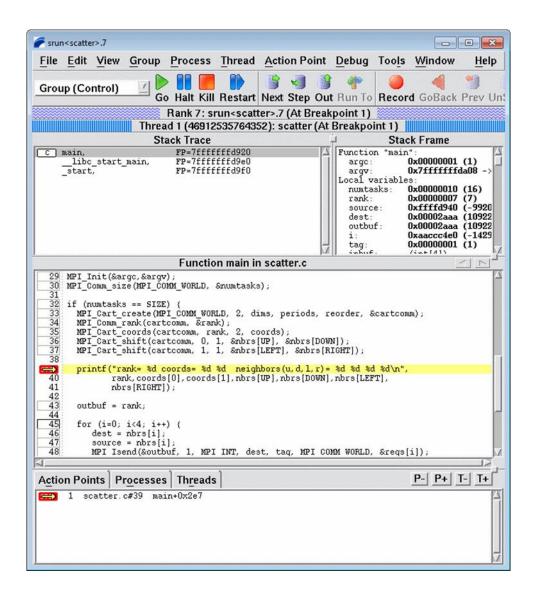

TotalView, mantida pela Rogue Wave Software, Inc, é uma ferramenta sofisticada para inspeção e análise de código (inclusive multithread). A TotalView fornece inspeção para códigos seriais, paralelos, multi-processos, *multithreads*,

aplicações aceleradas por GPU e aplicações híbridas escritas em C/C++ e Fortran, sendo possível utilizar tanto linha de comandos, quanto interface visual. Pode-se inspecionar programas, processos rodando e realizar depurações na memória. Na *Figura 2.12* apresenta-se o ambiente TotalView e análise de código MPI.

Figura 2.12 - Ferramenta TotalView analisando código MPI [Extraído de: (BARNEY,2015)]

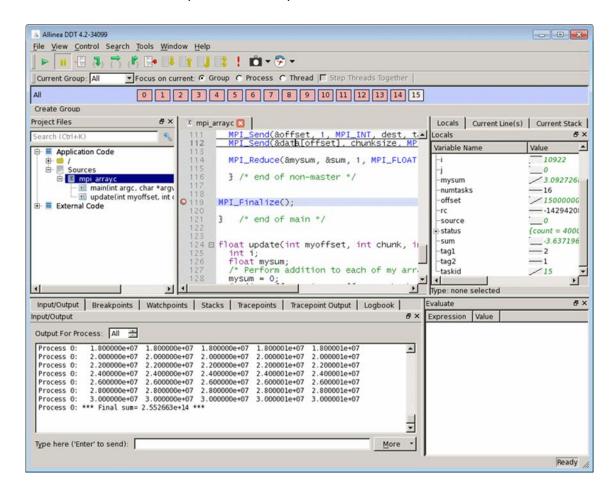

Outra importante ferramenta é a Allinea DDT, produto da Allinea Software Ltd., para inspeção de código com interface gráfica fácil de se usar, sendo capaz de inspecionar aplicações como: *multithread*, OpenMP, MPI, softwares heterogêneos que utilizam GPU, paradigmas híbridos como MPI+OpenMP ou MPI + CUDA, possui recursos de análise sintática destacando os potenciais erros no código fonte, além de

vir com depurador de memória embutido, integração de filas de mensagens MPI. Seus recursos estão disponíveis para as linguagens C/C++ e os derivados de Fortran, modelos de PGAs como UPC (*Unified Parallel C*) e Fotran 2008 Co-arrays, linguagens de GPU como HMPP, OpenMP *Accelerators*, CUDA e CUDA Fortran. Allinea DDT pode ser usada desde desktops até supercomputadores. Na *Figura 2.13* temos a interface do Allinea DDT ("Allinea DDT").

Figura 2.13 - Ferramenta Allinea DDT analisando código [Extraída de ("Allinea DDT")]

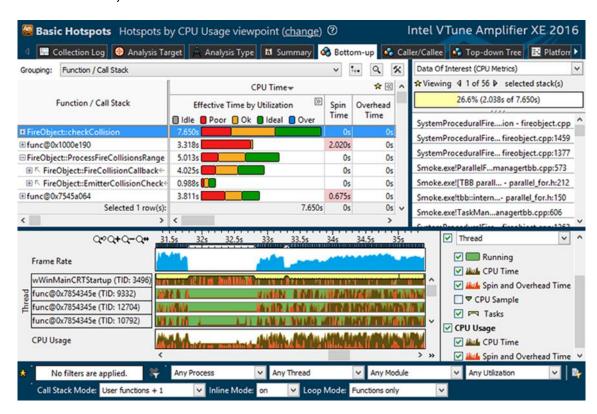

Intel Parallel Studio XE é um produto desenvolvido pela Intel, para facilitar o desenvolvimento em Windows e Linux de aplicações C/C+ e Fortran para aplicações paralelas. O Intel Parallel Studio XE é constituído pelos seguintes componentes (BLAIR; STOKES, 2012):

Intel Parallel Advisor: este componente dá conselhos de como adicionar paralelização ao programa.

- Intell Parallel Composer XE: o Composer XE contém o compilador e bibliotecas usadas para criar código otimizado e paralelo.

- Intel Parallel Inspector XE: é usado para checar os erros comuns de programa do tipo paralelo, tais erros como deadlocks, condições de corrida, erros de memória e vazamento de recursos tanto para programas paralelos como sequencias.

- Intel Vtune Amplifier XE é utilizado para analisar uma determinada aplicação e identificar os pontos críticos e gargalos. Esse componente analisa também o quão eficiente um programa paralelo é.

Abaixo temos a *Figura 2.14* com do ambiente Intel Parallel Studio XE ("Intel® Parallel Studio XE 2016").

Figura 2.14 - Ferramenta Intel Parallel Studio XE [Extraída de ("Intel® Parallel Studio XE 2016") ]

## Capítulo 3

### REVISÃO BIBLIOGRÁFICA

#### 3.1 Arquiteturas multicore recentes

A partir do marco de 2002, quando a IBM lançou o seu primeiro computador multicore o PowerPC 970, e outras fabricantes entram com produto multicore no mercado; como AMD em 2005 (Dual Core Opteron) e Intel em 2006 (Core Duo Pentium), constantes melhorias foram adicionadas, mais núcleos agregados a um mesmo chip, instruções vetoriais ampliadas, melhorias em barramentos de comunicação e mecanismos de coerência de cache.

Abaixo são apresentadas melhorias presentes em duas arquiteturas de servidores recentes: Intel Xeon 2600 – Sandy Bridge (2012) e AMD Opteron 6200 – Bulldozer (2011) a partir de dados obtidos em (MOLKA et al., 2014).

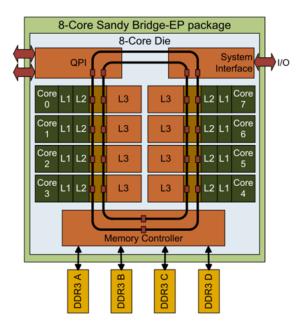

Intel Xeon 2600: é baseado na família da microarquitetura Sandy Bridge. Cada núcleo possui caches L1 e L2 dedicados, assim com sua própria FPU (floating-point unit - unidade de ponto flutuante). A FPU pode executar duas instruções de 256 bits por ciclo, uma adição e uma multiplicação. Através do HyperThreading dois threads podem ser executados por núcleo compartilhando a maioria dos recursos. Na Figura 3.1 extraída de (MOLKA et al., 2014), observa-se oito núcleos (cores), 20MB de cache L3, um canal quádruplo e duas interconexões QPI (QuickPath Interconnect).

Figura 3.1 - Processador 8 núcleos Sandy Bridge-EP [Extraído de: (MOLKA et al., 2014)]

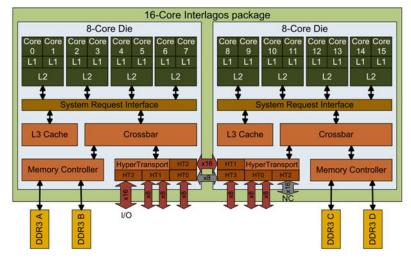

• AMD Opteron 6200: é baseado na microarquitetura Bulldozer. Esta microarquitetura baseia-se em unidades de computação de dois núcleos, que compartilham entre si unidades de carregamento e decodificação de instruções, unidade de ponto flutuante, além de cache L1 de instruções e cache L2. Cada núcleo possui sua própria unidade execução de operação com inteiros e cache L1 de dados. Cada cache de dados L1 possui duas portas de leitura de 128 bits e uma porta de escrita de 128 bits. A FPU proporciona a fusão de instruções de multiplicação e adição e executa duas instruções de 128 bits por ciclo. As instruções AVX, de 256 bits são divididas em duas partes de 128 bits. Instruções SIMD também são executadas na FPU compartilhada. Na Figura 3.2 temos a organização do AMD Opteron de dezesseis núcleos. Este processador consiste na ligação de dois blocos de oito núcleos através do barramento HyperTransport.

Figura 3.2 - Processador 16 núcleos Bulldozer. [Extraído de (MOLKA et al., 2014)].

#### 3.2 Arquitetura multicore de sistema embarcado recente

Existem inúmeras arquiteturas disponíveis para sistemas embarcados, cada uma dependente do escopo de atuação desse sistema. Em sua maioria construídas em SOC (*System on Chip*) que agrega CPUs, GPUs, controladores, caches e outros componentes de acordo com a aplicação que foram desenhados.

Da mesma forma que a arquitetura de computadores, a arquitetura da CPU dos sistemas embarcados evoluiu para os processadores multicores. A família de processadores ARM (*Advanced RISC Machine*) tem sido o componente mais comum dos SOC e como exemplo de arquitetura recente temos o processador Cortex-A72.

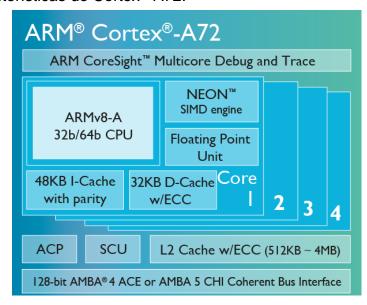

O processador Cortex-A72 ("Cortex-A72 Processor - ARM") é um processador de alto desempenho, lançado no início de 2015, baseado na arquitetura ARMv8, que tem de um a quatro *cores* (núcleos) SMP sendo capaz de executar instruções de 32 ou 64 bits. O processador tem disponível o recurso TrustZone que implementa em hardware o conceito da separação de aplicações seguras e não-seguras isoladas e os modos de operação, possui o recurso NEON para instruções SIMD avançadas de 128 bits e VFPv4 (*Vector Floating-Point*) que permite cálculos de precisão simples e dupla de ponto flutuante, além de suporte de hardware para virtualização, recurso CoreSight para inspeção e rastreamento em multicores. A *Figura* 3.3 representa os módulos e características do Cortex— A72.

Figura 3.3 – Estrutura e componentes do Cortex – A72 [Extraído de: ("Cortex-A72 Processor - ARM")]

O protocolo AMBA do processador Cortex-72 é um padrão aberto para a conexão e gerenciamento de blocos funcionais no SOC, além de facilitar o desenvolvimento de multiprocessador para um grande número de controladores e periféricos.

#### 3.3 Métodos para programação paralela em multicores

Para se aproveitar o potencial disponibilizado pelos processadores multicore, novos paradigmas foram criados e consequentemente novas ferramentas. As principais abordagens visaram a criação de modelos voltados para memória compartilhada, passagem de mensagens e modelo de dados paralelos.

No modelo de memória compartilhada, o paralelismo ocorre através de posições de memória compartilhadas entre os diversos processadores através de um mesmo barramento local que conecta processadores a memória. São exemplos de ferramentas e bibliotecas de memória compartilha:

- <u>Pthread</u>: é a biblioteca da linguagem C que define o uso de POSIX threads.

Esta biblioteca inclui desde criação de threads e sua destruição, gerenciamento de regiões críticas, uso de *locks*, *mutex* e semáforos.

- OpenMP: é uma API de desenvolvimento para as linguagens C/C++ e Fortran, na qual o gerenciamento de threads ocorre de maneira implícita através de diretivas de compilação e uso de bibliotecas.

No modelo de passagem de mensagens, a organização, paralelização e divisão das tarefas ocorre por meio de trocas de mensagens. Esse modelo favorece a utilização de sistemas distribuídos, embora possa ser utilizado com arquiteturas de memória compartilhada. Como exemplo de padronização de passagem de mensagens:

MPI: é um padrão de bibliotecas para passagem de mensagens, fornecendo suporte a mensagens ponto a ponto, como mensagens globais. Em MPI o gerenciamento é feito de maneira implícita, cabendo ao programador especificar quais tarefas serão executadas e em quais processos. As implementações desse padrão estão disponíveis para as linguagens C/C++ e Fortran. As distribuições mais conhecidas são: GridMPI, LAM/MPI, OpenMPI, MPICH e MVAPICH.

No modelo de dados paralelos, também conhecido como PGA (*Partitioned Global Address Space*), temos um espaço de endereço global. Os grupos de tarefas trabalham coletivamente executando uma mesma operação em diferentes áreas de um mesmo arranjo de dados. As principais implementações são: Co-Array Fortran, Titanium, Unified Parallel C, Chapel, X10 e Fortress.

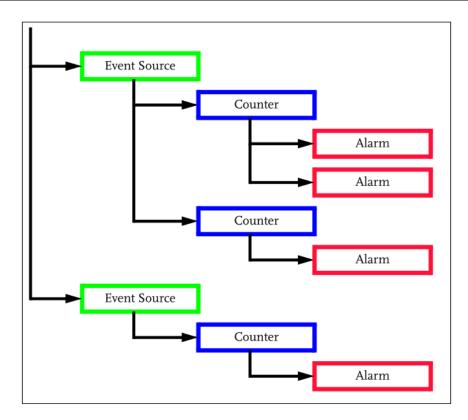

A partir da combinação de modelos paralelos existentes descritos anteriormente, novas possibilidades vêm surgindo nos denominados modelos híbridos. A ideia é mesclar arquiteturas heterogêneas, buscando aproveitar melhor o poder computacional e recursos disponíveis: