Universidade Federal de São Carlos Centro de Ciências Exatas e de Tecnologia Programa de Pós-Graduação em Engenharia Elétrica

Wenzel Maier

# High Integrated Battery Monitoring System with Active Balancing up to $\pm 10 \text{ A}$

Wenzel Maier

# High Integrated Battery Monitoring System with Active Balancing up to $\pm 10 \text{ A}$

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica do Centro de Ciências Exatas e de Tecnologia da Universidade Federal de São Carlos, como parte dos requisitos para a obtenção do título de Mestre em Engenharia Elétrica.

Área de concentração: Sistemas Elétricos e Eletrônicos

Orientador: Prof. Dr. Amilcar F. Querubini Gonçalves Coorientador: Prof. Dr. Ricardo Quadros Machado

# UNIVERSIDADE FEDERAL DE SÃO CARLOS

Centro de Ciências Exatas e de Tecnologia Programa de Pós-Graduação em Engenharia Elétrica

## Folha de Aprovação

Defesa de Dissertação de Mestrado do candidato Wenzel Maier, realizada em 22/02/2022.

## Comissão Julgadora:

Prof. Dr. Amilcar Flamarion Querubini Gonçalves (UFSCar)

Prof. Dr. Flávio Alessandro Serrão Gonçalves (UNESP)

Prof. Dr. José Roberto Boffino de Almeida Monteiro (USP)

O Relatório de Defesa assinado pelos membros da Comissão Julgadora encontra-se arquivado junto ao Programa de Pós-Graduação em Engenharia Elétrica.

This work is dedicated to my grandfather *Wenzel Krobath* (30.8.1915 - 1.1.2004). I am pleased and proud to have met this great man.

## ACKNOWLEDGEMENT

I would like to thank *Prof. Dr. Amilcar F. Q. Gonçalves* and *Prof. Dr. Ricardo Quadros Machado*, who made a significant contribution to the success of this thesis through their personal support during the corona pandemic.

I would also like to thank the *Universidade Federal de São Carlos* and the entire Department of Electrical Engineering, who contributed to my academic education.

Special thanks go to my in-laws, *Maria Olga M. da Silva* and *João R. da Silva*, who encouraged me in my actions and were a welcome balance to the electronic routine.

My biggest thanks go to my wife Juliana Maria da Silva, who always supported me with the start, organization and execution of the master's course. Without her explanations of the structure and regulations of the Brazilian higher education system, as well as the understandable translation of the university regulations, this project would not have come about. I would also like to thank her for her patience and calm with me and my great electronic chaos, especially when something didn't work as desired.

## RESUMO

MAIER, Wenzel. Sistema Altamente Integrado com Balanceamento Ativo e Monitoramento de Baterias de até ±10 A. 2022. 114 f. Dissertação de Mestrado – Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal de São Carlos. São Carlos -SP, 2022.

Esta dissertação de mestrado descreve o desenvolvimento, construção e estrutura de um sistema altamente integrado, flexível e modular de monitoramento de baterias. A unidade eletrônica usa um processo de balanceamento ativo com correntes de até  $\pm 10$  A para redistribuir e equilibrar a energia elétrica dentro de uma pilha de bateria. Para poder carregar e descarregar uma célula do acumulador com esta alta corrente é necessário um conversor CC/CC isolado galvanicamente, que possa transferir energia bidirecionalmente e com baixas perdas. A saída deste conversor é conectada a um multiplexador de potência que seleciona, de maneira direcionada, uma determinada célula do acumulador da bateria, permitindo realizar a medição da tensão da célula, bem como o fluxo de energia bidirecional. Isso permite que a unidade conversora CC/CC seja usada em conjunto por várias células que estão conectadas em série na bateria, reduzindo consideravelmente o custo e o espaço de instalação.

Enquanto o multiplexador tem uma construção o mais simples possível para manter baixo o custo de implementação, o conversor CC/CC bidirecional usa dois estágios de conversão simples, mas altamente eficientes, para implementar a separação de potencial e a adaptação da tensão à célula da bateria. A função e a estrutura desses dois estágios do conversor, independentes um do outro, são tratados em detalhes neste trabalho, com um modelo matemático que descreve também a interação de todo o sistema de gerenciamento de baterias. Além do mais, são apresentados e descritos todos os módulos periféricos, como a fonte auxiliar, a unidade de medição analógica, a unidade de comunicação e a unidade de controle digital do conversor CC/CC.

O desempenho do sistema proposto é comprovado por medições em um protótipo. Com base na potência de entrada e saída, a eficiência, bem como a perda de potência do conversor CC/CC, do multiplexador e de toda a eletrônica das placas foram determinadas. O sistema de gerenciamento de bateria implementado permite balancear a célula selecionada com uma eficiência de até 85% em um curto espaço de tempo. Além disso, a medição da tensão da célula, que é particularmente importante para monitorar a bateria, foi verificada e testada. Após ajustar o sistema, é possível realizar uma medição de tensão com uma resolução de  $\pm 500 \,\mu$ V. Isso permite que o estado de carga de cada célula seja determinado individualmente com um alto grau de precisão.

**Palavras-chave**: gerenciamento de bateria, monitoramento de células, balanceamento ativo, conversor bidirecional CC/CC, multiplexador de potência

## ABSTRACT

MAIER, Wenzel. High Integrated Battery Monitoring System with Active Balancing up to  $\pm 10$  A. 2022. 114 f. Dissertação de Mestrado – Programa de Pós-Graduação em Engenharia Elétrica, Universidade Federal de São Carlos. São Carlos - SP, 2022.

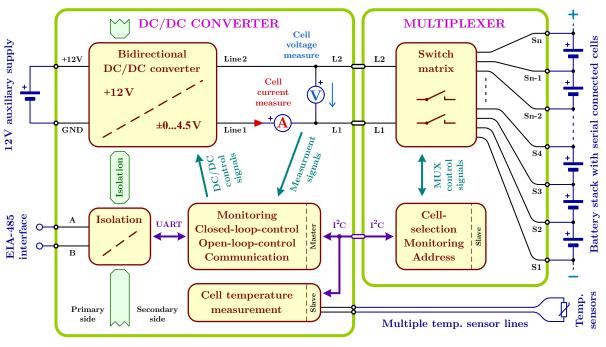

This master's thesis describes the development, construction, and setup of a flexible and modular, highly integrated battery monitoring system. The electronic unit uses an active balancing process with currents up to  $\pm 10$  A to redistribute and balance the electrical energy within a battery stack. In order to be able to charge and discharge an accumulator cell with this high current, a galvanic isolated DC/DC converter is necessary, which can transfer energy bidirectionally with low losses. The output of this converter is connected to a power multiplexer, which selects a desired accumulator cell of the battery stack in a targeted manner. This enables the cell voltage to be measured and the flow of energy to or from the cell. This allows the DC/DC converter unit to be used jointly by several accumulator cells connected in series, thereby reducing installation space and costs considerably.

While the multiplexer has a structure that is as simple as possible to keep the outlay for implementation low, the bidirectional DC/DC converter uses two highly efficient converter stages to implement the potential separation and the voltage adjustment to the accumulator cell. The function and structure of these two converter stages, which are independent of one another, are dealt with in detail in this work, with a mathematical model also describing the interaction of the entire battery management system. Furthermore, all peripheral modules, such as auxiliary power supply, analog measuring unit, communication and digital control unit, of the DC/DC converter module are presented and explained.

The performance of the presented concept is proven by measurements on a hardware prototype. Based on the input and output power, the efficiency as well as the power loss of the DC/DC converter, the multiplexer and the entire electronic were determined. The implemented battery management system allows the selected cell to be balanced in a short time with an efficiency of up to 85 %. In addition, the cell voltage measurement, which is particularly important for monitoring the battery, was checked and tested. After adjusting the electronic, a voltage measurement with a resolution of  $\pm 500 \,\mu\text{V}$  is possible. This allows the state of charge of each individual cell to be determined with great accuracy.

**Keywords**: battery management, cell monitoring, active balancing, bidirectional DC/DC converter, power multiplexer

# LIST OF FIGURES

| Figure 1 – Discharge curve of a LiFePO <sub>4</sub> cell - example $\ldots \ldots \ldots \ldots \ldots \ldots$                        | 4  |

|---------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 – Cell under-voltage                                                                                                         | 5  |

| Figure 3 – Cell over-voltage                                                                                                          | 5  |

| Figure 4 $-$ Balancing process - equalization of cell capacity $\ldots \ldots \ldots \ldots$                                          | 5  |

| Figure 5 – Discharge stop $\ldots$                   | 6  |

| Figure 6 – Charge stop $\ldots$                      | 6  |

| Figure 7 – Cell balancing techniques overview                                                                                         | 7  |

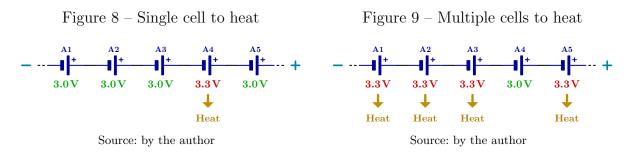

| Figure 8 – Single cell to heat                                                                                                        | 7  |

| Figure 9 – Multiple cells to heat $\ldots$           | 7  |

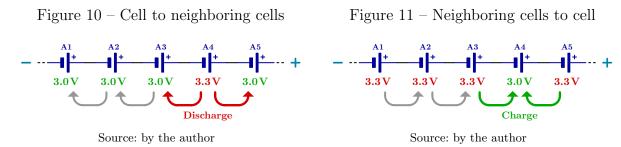

| Figure $10$ – Cell to neighboring cells $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | 8  |

| Figure $11$ – Neighboring cells to cell $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$              | 8  |

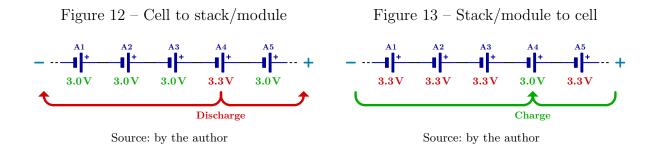

| Figure 12 – Cell to stack/module $\ldots$            | 10 |

| Figure $13 - \text{Stack/module to cell}$                                                                                             | 10 |

| Figure 14 – Cell to auxiliary source $\ldots$        | 11 |

| Figure 15 – Auxiliary source to cell                                                                                                  | 11 |

| Figure 16 – Basic block diagram of the balancer electronic $\ldots \ldots \ldots \ldots \ldots \ldots$                                | 19 |

| Figure 17 – Power multiplexer structure                                                                                               | 20 |

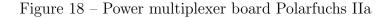

| Figure 18 – Power multiplexer board Polarfuchs IIa                                                                                    | 21 |

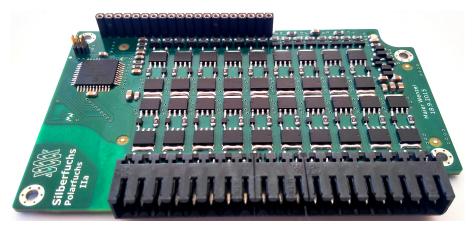

| Figure 19 – DC/DC converter structure $\ldots \ldots \ldots$           | 23 |

| Figure $20 - L1/C1$ plus damping resistors $\ldots \ldots \ldots$      | 23 |

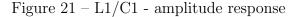

| Figure $21 - L1/C1$ - amplitude response $\ldots \ldots \ldots$ | 23 |

| Figure 22 – Push-pull converter structure - idealized                                                                                 | 25 |

| Figure 23 – Push-pull converter - voltages                                                                                            | 25 |

| Figure 24 – Push-pull converter - currents                                                                                            | 25 |

| Figure 25 – Full-bridge structure - idealized                                                                                         | 27 |

| Figure 26 – Buck converter mode                                                                                                       | 28 |

| Figure 27 – Boost converter mode                                                                                                      | 28 |

| Figure 28 – Synchronous converter mode                                                                                                | 29 |

| Figure 29 – Positive and negative currents                                                                                            | 29 |

| Figure 30 – Simplified closed-loop control structure                                                                                  | 31 |

| Figure $31$ – Simple block diagram of the power stages $\ldots \ldots \ldots \ldots \ldots \ldots \ldots$                             | 33 |

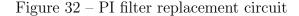

| Figure 32 – PI filter replacement circuit                                                                                             | 34 |

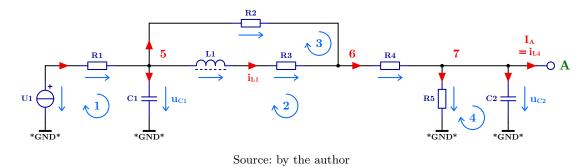

| Figure 33 – Push-pull converter replacement circuit                                                                                   | 36 |

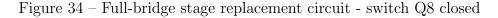

| Figure 34 – Full-bridge stage replacement circuit - switch Q8 closed $\ldots$ $\ldots$ $\ldots$                                       | 38 |

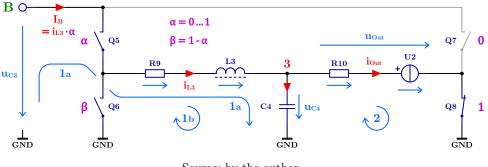

| Figure 35 – Pode-plot of the transfer functions $i_{Out,1}/\alpha$ (red) and $u_{Out,1}/\alpha$ (blue) .                              | 44 |

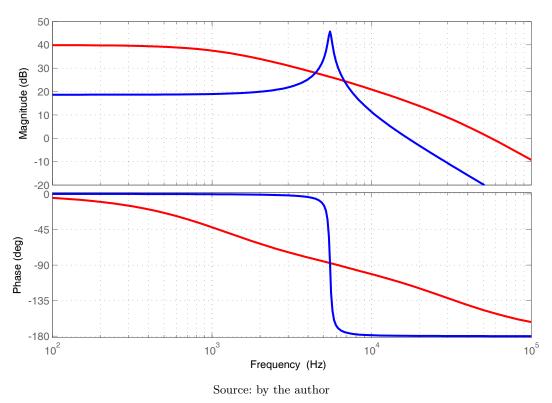

| Figure 36 – Full-bridge stage replacement circuit - switch Q7 closed $\ldots$ $\ldots$ $\ldots$                                       | 45 |

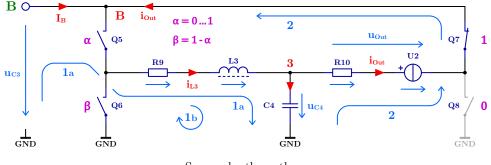

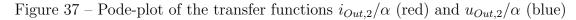

| Figure 37 – Pode-plot of the transfer functions $i_{Out,2}/\alpha$ (red) and $u_{Out,2}/\alpha$ (blue)                                                                               | . 46 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

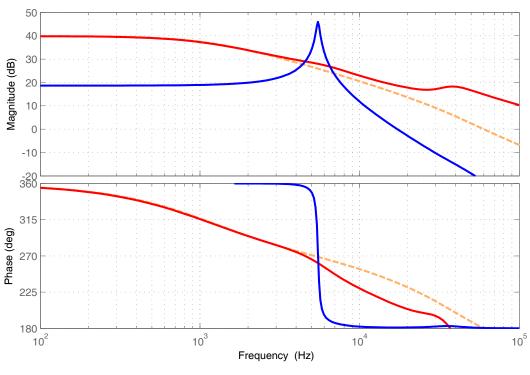

| Figure 38 – DC/DC converter board Platinfuchs IIa                                                                                                                                    | . 47 |

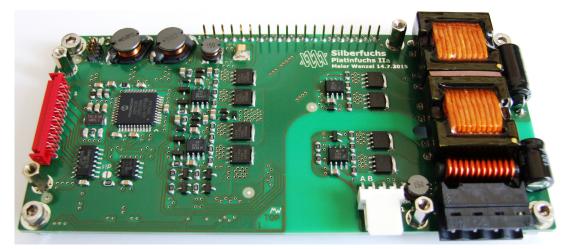

| Figure 39 – Input stage with PI filter and fuse indicator                                                                                                                            | . 48 |

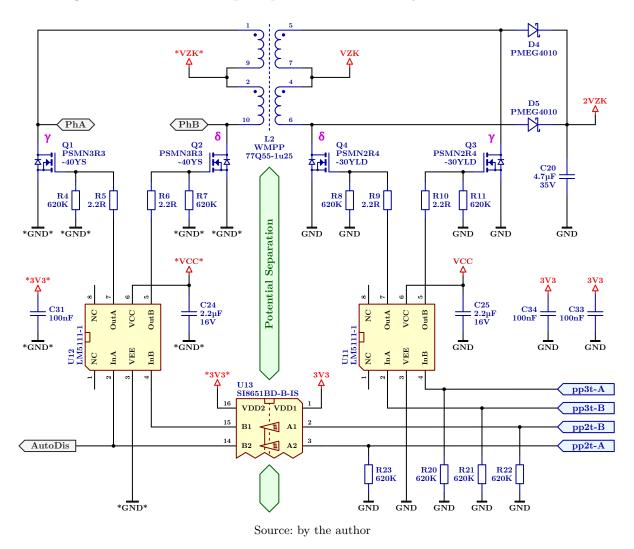

| Figure 40 – Bidirectional push-pull converter with synchronous rectification $\ldots$ .                                                                                              | . 50 |

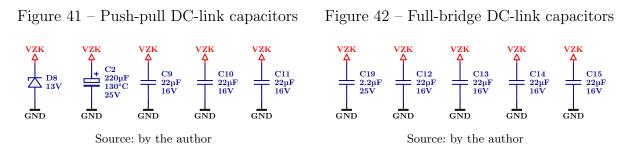

| Figure 41 – Push-pull DC-link capacitors                                                                                                                                             | . 51 |

| Figure 42 – Full-bridge DC-link capacitors                                                                                                                                           | . 51 |

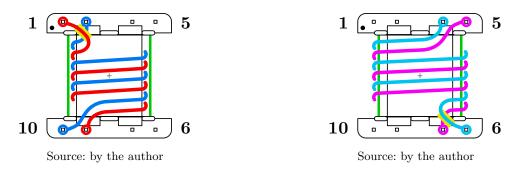

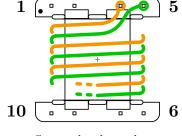

| Figure 43 – Winding scheme, primary side                                                                                                                                             | . 52 |

| Figure 44 – Winding scheme, secondary side                                                                                                                                           | . 52 |

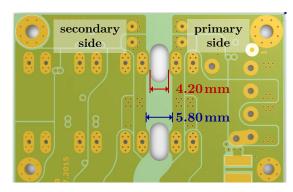

| Figure 45 – Clearance and creepage distances                                                                                                                                         | . 55 |

| Figure 46 – Autostart self oscillating circuit                                                                                                                                       | . 56 |

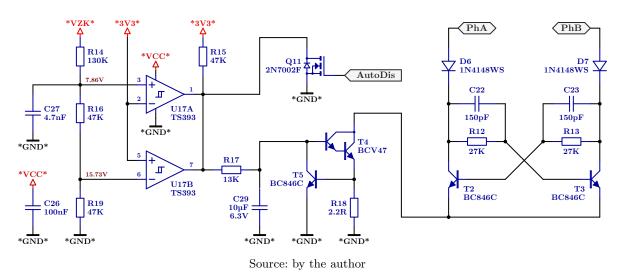

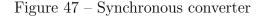

| Figure 47 – Synchronous converter                                                                                                                                                    | . 57 |

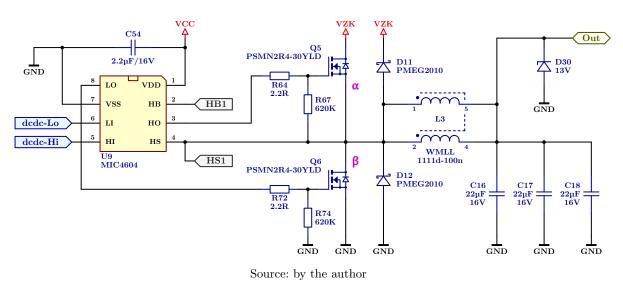

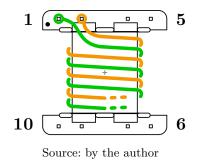

| Figure 48 – Winding scheme, bottom layer                                                                                                                                             | . 59 |

| Figure 49 – Winding scheme, top layer                                                                                                                                                | . 59 |

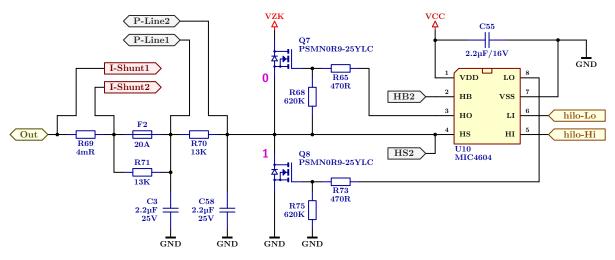

| Figure 50 – High-low selection                                                                                                                                                       | . 61 |

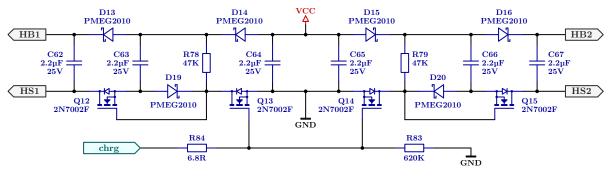

| Figure 51 – Double charge-pump                                                                                                                                                       | . 62 |

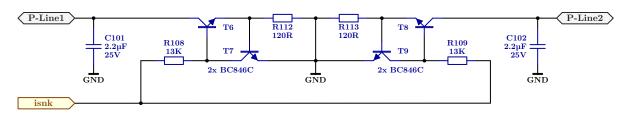

| Figure 52 – Current-sink circuit                                                                                                                                                     | . 63 |

| Figure 53 – Cell voltage measurement                                                                                                                                                 | . 64 |

| Figure 54 – Cell current measurement                                                                                                                                                 | . 66 |

| Figure 55 – DC-link voltage and additional measurements                                                                                                                              | . 66 |

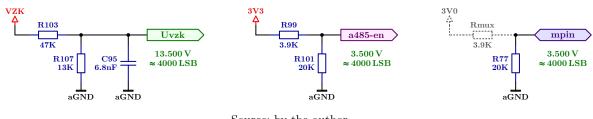

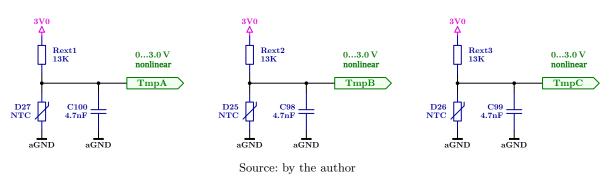

| Figure 56 – On-board temperature measurement                                                                                                                                         | . 67 |

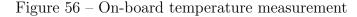

| Figure 57 – External temperature measurement                                                                                                                                         | . 68 |

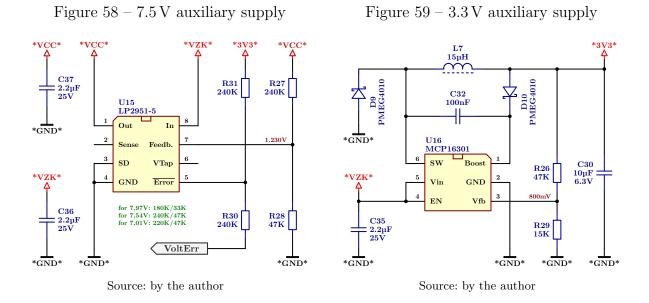

| Figure 58 – 7.5 V auxiliary supply $\ldots \ldots \ldots$                                                             | . 72 |

| Figure 59 – $3.3 \mathrm{V}$ auxiliary supply $\ldots \ldots \ldots$ | . 72 |

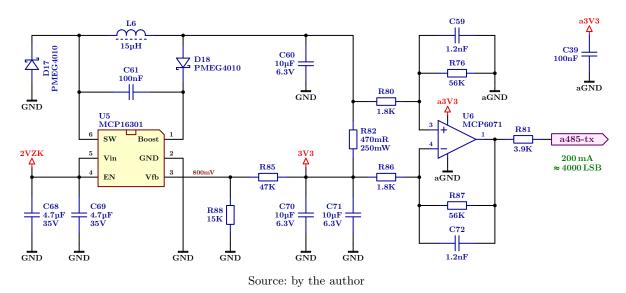

| Figure $60 - 3.3$ V auxiliary supply with current monitoring                                                                                                                         | . 72 |

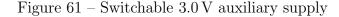

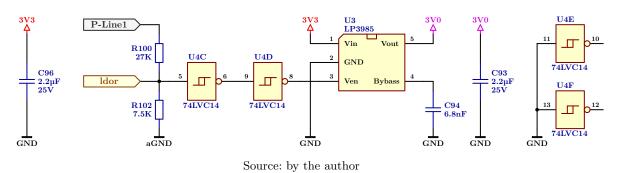

| Figure 61 – Switchable 3.0 V auxiliary supply                                                                                                                                        | . 73 |

| Figure 62 – VCC boost converter                                                                                                                                                      | . 74 |

| Figure 63 – VDD boost converter                                                                                                                                                      | . 76 |

| Figure 64 – 16-bit dsPIC33EP128GM304 microcontroller                                                                                                                                 | . 77 |

| Figure $65 - 8.0 \mathrm{MHz}$ quartz $\ldots \ldots \ldots$         | . 78 |

| Figure 66 – Non-volatile memory                                                                                                                                                      | . 78 |

| Figure 67 – EIA-485 interface                                                                                                                                                        | . 79 |

| Figure 68 – 3.0 V, $\pm 0.1$ % voltage reference                                                                                                                                     | . 80 |

| Figure 69 – Connector position on the Platinfuchs IIa board                                                                                                                          | . 83 |

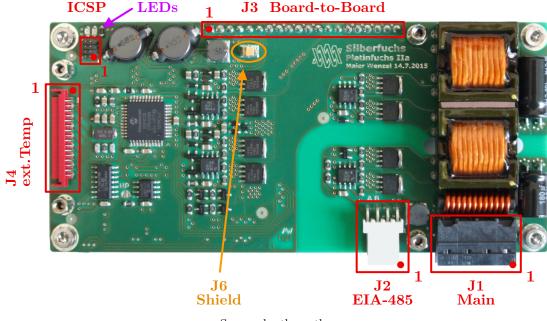

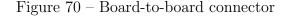

| Figure 70 – Board-to-board connector                                                                                                                                                 | . 84 |

| Figure 71 – Temp. sensor connector                                                                                                                                                   | . 85 |

| Figure 72 – ICSP programming connector                                                                                                                                               | . 85 |

| Figure 73 – Conductor paths on the TOP-, MD1-, MD2- and BOT-layers                                                                                                                   | . 87 |

| Figure 74 – Component position on the top                                                                                                                                            | . 89 |

| Figure 75 – Component position on the bottom                                                                                                                                         | . 90 |

| Figure | 76 – | Voltage step - Calculation                                                                                                                                                                    |

|--------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Figure | 77 - | Voltage step - Hardware $\dots \dots \dots$                                                   |

| Figure | 78 - | Current step - Calculation                                                                                                                                                                    |

| Figure | 79 - | Current step - Hardware                                                                                                                                                                       |

| Figure | 80 - | Measurement deviation due to the multiplexer board                                                                                                                                            |

| Figure | 81 - | One sample measured; full-bridge enabled                                                                                                                                                      |

| Figure | 82 - | One sample measured; full-bridge disabled                                                                                                                                                     |

| Figure | 83 - | Measured voltage jitter; full-bridge enabled                                                                                                                                                  |

| Figure | 84 - | Measured voltage jitter; full-bridge disabled                                                                                                                                                 |

| Figure | 85 - | Average of 32 samples; full-bridge enabled                                                                                                                                                    |

| Figure | 86 - | Average of 32 samples; full-bridge disabled                                                                                                                                                   |

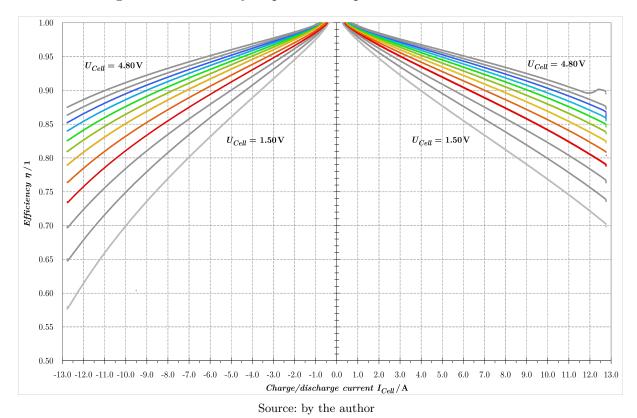

| Figure | 87 - | Efficiency of DC/DC converter board Platinfuchs IIa                                                                                                                                           |

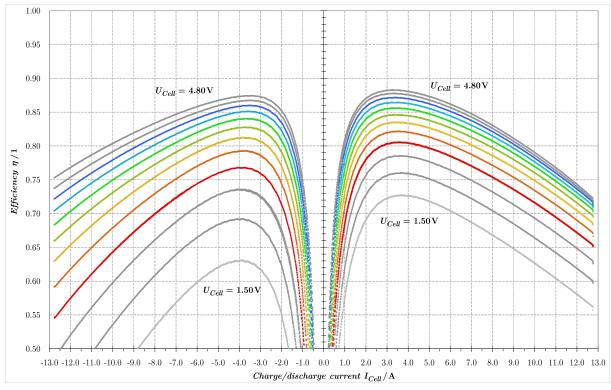

| Figure | 88 - | Efficiency of power multiplexer board Polarfuchs IIa                                                                                                                                          |

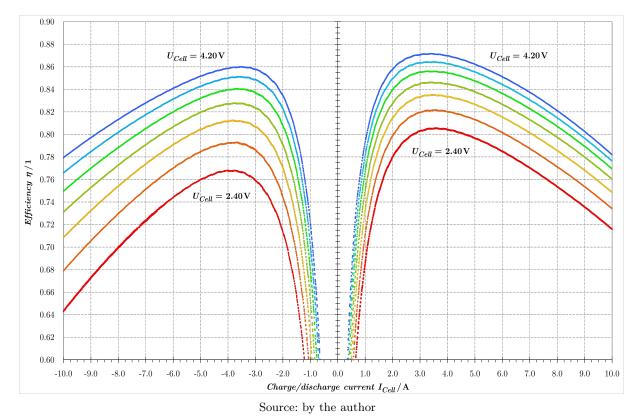

| Figure | 89 - | Efficiency of the total electronic (Silberfuchs balancer) 100                                                                                                                                 |

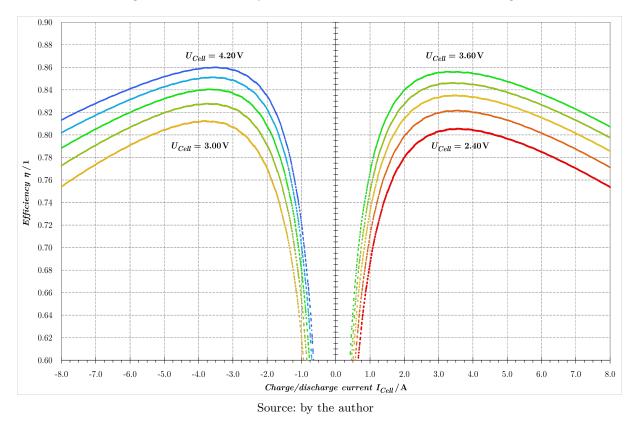

| Figure | 90 - | Efficiency of the total electronic - $\pm 10.0$ A range                                                                                                                                       |

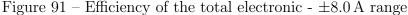

| Figure | 91 - | Efficiency of the total electronic - $\pm 8.0$ A range $\ldots \ldots \ldots$ |

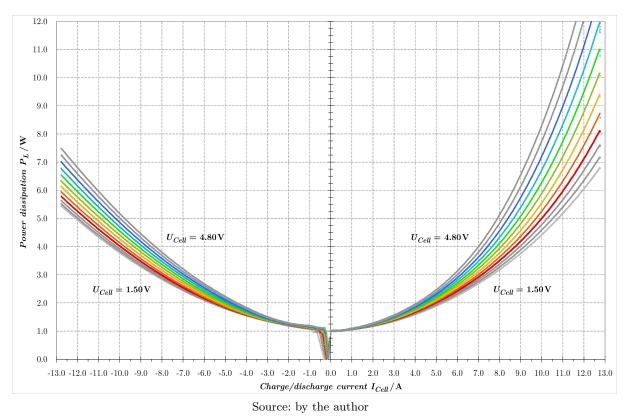

| Figure | 92 - | Power loss of DC/DC converter board Platin<br>fuchs IIa                                                                                                                                       |

| Figure | 93 - | Power loss of power multiplexer board Polarfuchs IIa $\ldots \ldots \ldots \ldots \ldots 103$                                                                                                 |

| Figure | 94 - | Power loss of the total electronic (Silberfuchs balancer) $\ldots \ldots \ldots \ldots 103$                                                                                                   |

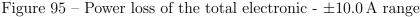

| Figure | 95 - | Power loss of the total electronic - $\pm 10.0$ A range                                                                                                                                       |

| Figure | 96 - | Power loss of the total electronic - mathematical model 105                                                                                                                                   |

# LIST OF TABLES

| Table 1 –   | Typical cell voltages of different lithium-based accumulator cells              | 4  |

|-------------|---------------------------------------------------------------------------------|----|

| Table 2 $-$ | Comparison of cell balancing techniques                                         | 12 |

| Table 3 $-$ | Four-quadrant operating states of the closed-loop control                       | 32 |

| Table 4 –   | PI filter replacement circuit - element description                             | 35 |

| Table 5 $-$ | Push-pull converter replacement circuit - element description                   | 36 |

| Table 6 –   | Full-bridge stage replacement circuit - element description                     | 38 |

| Table 7 $-$ | Winding characteristics of transformer WMPP77Q55-1u25                           | 53 |

| Table 8 –   | Winding characteristics of transformer WMPP66Q44-1u25                           | 54 |

| Table 9 $-$ | Possible turns and associated values for the storage choke $\ldots$             | 60 |

| Table 10 –  | External temperature measurement - 1st and 2nd functions $\ldots \ldots \ldots$ | 70 |

| Table 11 –  | Digital control system - 1st function                                           | 81 |

| Table 12 –  | Digital control system - 2nd function                                           | 82 |

| Table 13 –  | Copper layers and their functions on the Platinfuchs IIa board $\ldots$ .       | 86 |

|             |                                                                                 |    |

# LIST OF ABBREVIATIONS AND ACRONYMS

| 5000 +                                      | price refers to 5000 or more units                                |

|---------------------------------------------|-------------------------------------------------------------------|

| AC                                          | alternating current (voltage)                                     |

| ADC                                         | analog-to-digital converter                                       |

| AFE                                         | analog front-end                                                  |

| BOT                                         | bottom layer of the PCB                                           |

| CC-CV                                       | constant current - constant voltage charging (discharging) method |

| CCM                                         | continuous current mode                                           |

| CMOS                                        | complementary metal–oxide–semiconductor                           |

| DC                                          | direct current (voltage)                                          |

| DCM                                         | discontinuous current mode                                        |

| DNL                                         | differential nonlinearity of ADC                                  |

| EIA-485                                     | also known as RS-485, TIA-485 or ANSI-485                         |

| ELV                                         | extra-low voltage (IEC 60449)                                     |

| ESL                                         | equivalent series inductance of capacitor                         |

| ESR                                         | equivalent series resistance of capacitor                         |

| EEPROM                                      | electrically erasable programmable read-only memory               |

| $I^2C$                                      | inter-integrated circuit                                          |

| ICSP                                        | in-circuit serial programming interface (Microchip)               |

| INL                                         | integral nonlinearity of ADC                                      |

| LC                                          | inductor-capacitor resonant circuit                               |

| LDO                                         | low-dropout regulator                                             |

| LED                                         | light-emitting diode                                              |

| $\rm Li_4Ti_5O_{12}$                        | lithium-titanate-oxide accumulator                                |

| $LiCoO_2$                                   | lithium-cobalt-oxide accumulator                                  |

| $\rm LiFePO_4$                              | lithium-iron-phosphate accumulator                                |

| $\rm LiMn_2O_4$                             | lithium-manganese-oxide accumulator                               |

| $\rm LiNiCoAlO_2$                           | lithium-nickel-cobalt-aluminum-oxide accumulator                  |

| $LiNiMnCoO_2$                               | lithium-nickel-manganese-oxide accumulator                        |

| $\mathrm{Li}_4\mathrm{Ti}_5\mathrm{O}_{12}$ | lithium-titanate-oxide accumulator                                |

| LSB                                         | least significant bit                                             |

| LUT                                         | lookup table                                                      |

| MD1                                         | first middle layer of the PCB                                     |

| MD2                                         | second middle layer of the PCB                                    |

|                                             |                                                                   |

| MIPS   | millions of instructions per second                  |

|--------|------------------------------------------------------|

| MOS    | metal-oxide-semiconductor technology                 |

| MOSFET | metal–oxide–semiconductor field-effect transistor    |

| MSB    | most significant bit                                 |

| NTC    | negative temperature coefficient thermistor          |

| PCB    | printed circuit board                                |

| PID    | proportional-integral-differential controller        |

| PTC    | positive temperature coefficient thermistor          |

| PWM    | pulse-width modulation                               |

| RC     | resistor-capacitor filter circuit                    |

| RTD    | resistance temperature detectors (PT1000 or similar) |

| SoC    | state of charge of an electric battery system        |

| SoH    | state of health of an electric battery system        |

| SoS    | state of safety of an electric battery system        |

| SMD    | surface mount device                                 |

| THT    | through hole technology                              |

| TOP    | top layer of PCB                                     |

| TQFP   | thin quad flat package                               |

| TVS    | transient-voltage-suppression diode                  |

| UART   | universal asynchronous receiver-transmitter          |

Important potential labels on the primary side:

| *3V3*          | 3.3 V auxiliary supply                       |

|----------------|----------------------------------------------|

| *GND*          | reference potential (ground)                 |

| * <i>VCC</i> * | output of low drop-out regulator LP2951-5 $$ |

| *VZK*          | potential of intermediate circuit            |

- Important potential labels on the secondary side:

| 2VZK | double potential of $VZK$                   |

|------|---------------------------------------------|

| 3V0  | switchable $3.0\mathrm{V}$ auxiliary supply |

| 3V3  | 3.3 V auxiliary supply                      |

| aVCC | auxiliary supply for analog front-end stage |

| a3V3 | analog 3.3 V auxiliary supply               |

| aGND | analog reference potential (analog ground)  |

| GND  | reference potential (ground)                |

| HS1       | switching note at synchronous converter (full-bridge)      |

|-----------|------------------------------------------------------------|

| HS2       | switching note at high-low selection circuit (full-bridge) |

| <i>L1</i> | Line1 at synchronous converter (full-bridge)               |

| L2        | Line2 at high-low selection circuit (full-bridge)          |

| Out       | output (respectively input) of the synchronous converter   |

| VCC       | output of VCC boost converter                              |

| VDD       | output of VDD boost converter                              |

| VZK       | potential of intermediate circuit                          |

|           |                                                            |

- Further label names can be read directly from the circuit diagrams.

# LIST OF SYMBOLS

- General math acronyms:

|                 | mathematical operator: "normal" multiplication or matrix multiplication                                       |

|-----------------|---------------------------------------------------------------------------------------------------------------|

|                 | mathematical operator: $R_1    R_2       R_n = \frac{1}{1/R_1 + 1/R_2 + + 1/R_n}$                             |

| ω               | angular frequency: $\omega = 2 \cdot \pi \cdot f$                                                             |

| j               | imaginary unit: $j = \sqrt{-1}$                                                                               |

| S               | complex frequency parameter: $s = j \cdot \omega + \sigma$ , with $\sigma = 0 \rightarrow s = j \cdot \omega$ |

| x               | variable - variable over time (changes within a period)                                                       |

| X               | variable - constant over time (constant over at least one period)                                             |

| X               | matrix or vector - constant over time/frequency                                                               |

| x(s)            | variable - variable over frequency                                                                            |

| $\mathbf{x}(s)$ | vector - variable over frequency                                                                              |

| x(t)            | variable - variable over time (equal to $x$ )                                                                 |

| $\mathbf{x}(t)$ | vector - variable over time                                                                                   |

| $\mathbf{X}^T$  | transposed matrix/vector - constant over time/frequency                                                       |

| $X_{'Y'}$       | component designation 'Y' - e.g. $R_{R1}$ is the resistance of resistor R1                                    |

| $X'_{Z'}$       | potential designation 'Z' - e.g. $U_{VZK}$ is the voltage of the $VZK$ potential                              |

|                 |                                                                                                               |

- Specific electrotechnical acronyms:

| %            | in the schematic diagrams indicates high-precision resistors            |

|--------------|-------------------------------------------------------------------------|

| $\epsilon_r$ | relative permittivity                                                   |

| $\eta$       | efficiency factor                                                       |

| $\mu_0$      | vacuum permeability: $\mu_0 = 4 \cdot \pi \cdot 10^{-7} \mathrm{N/A^2}$ |

| $	au_{Sync}$ | time constant of the synchronous converter                              |

| α            | duty cycle of the synchronous converter switch $Q5$                     |

| $\beta$      | duty cycle of the synchronous converter switch Q6                       |

| $\gamma$     | duty cycle of the push-pull converter switches Q1 and Q3 $$             |

| δ            | duty cycle of the push-pull converter switches $Q2$ and $Q4$            |

| $A_e$        | cross-section of EFD20 ferrite core                                     |

| $A_L$        | magnetic conductance of ferrite core                                    |

| $B_{max}$    | maximum magnetic flux density in the ferrite core                       |

| $B_{sat}$    | maximum allowable magnetic flux density before saturation occurs        |

| C            | generally capacity (also C-rate of an accumulator cell)                 |

| E                | generally energy                                                           |

|------------------|----------------------------------------------------------------------------|

| $f_{cut,1}$      | -3dB cut-off frequency of measurement amplifier stage - first stage        |

| $f_{cut,2}$      | -3dB cut-off frequency of measurement amplifier stage - second stage       |

| $f_{cut,3}$      | -3dB cut-off frequency of measurement amplifier stage - output             |

| $f_{res,Sync}$   | resonance frequency of the synchronous converter - LC resonant circuit     |

| $f_{sw}$         | switching frequency of push-pull and synchronous converter                 |

| Ι                | generally current                                                          |

| $I_{\Delta}$     | ripple current in a power inductor                                         |

| $I_A$            | auxiliary variable - later be replaced by the corresponding expression     |

| $I_B$            | auxiliary variable - later be replaced by the corresponding expression     |

| $I_{Cell}$       | charge/discharge current of the accumulator cell (equal to $I_{Out}$ )     |

| $I_D$            | drain current of a MOSFET                                                  |

| $I_{DC}$         | direct current without ripple in a power inductor                          |

| $I_{leak}$       | leakage current between primary and secondary side of a transformer        |

| $I_{max}$        | maximum current that occurs during operation                               |

| $I_{op}$         | operating current of a semiconductor                                       |

| $I_{Out}$        | output (input) current of the cell balancer circuit (equal to $I_{Cell}$ ) |

| $I_{Set,neg}$    | negative current setpoint value of the closed-loop control                 |

| $I_{Set,pos}$    | positive current setpoint value of the closed-loop control                 |

| $I_{Switch}$     | current consumption of bidirectional power switch (power multiplexer)      |

| k                | turn ratio of a transformer: $k = n_{sec}/n_{pri}$                         |

| L                | generally inductance                                                       |

| $L_{\sigma,pri}$ | transformer leakage inductance - primary side                              |

| $l_{air}$        | air gap in the ferrite core                                                |

| $L_{M,pri}$      | transformer main inductance - primary side                                 |

| n                | generally number of turns of a coil (inductor or transformer)              |

| $n_{pri}$        | number of turns of a transformer - primary side                            |

| $n_{sec}$        | number of turns of a transformer - secondary side                          |

| Р                | generally power                                                            |

| $P_L$            | thermal power loss                                                         |

| Q                | generally charge                                                           |

| $Q_G$            | gate charge of a power MOSFET                                              |

| R                | generally resistance                                                       |

| $R_{Cu}$         | copper resistance of a conductor path on the PCB                           |

| $R_{pri}$        | copper resistance of a transformer - primary side                          |

| $R_{sec}$        | copper resistance of a transformer - secondary side                        |

| $R_{DSon}$ | drain-source switch-on resistance of a power MOSFET           |

|------------|---------------------------------------------------------------|

| t          | generally time                                                |

| U          | generally voltage                                             |

| $U_{Bat+}$ | positive voltage of the whole battery                         |

| $U_{Bat-}$ | negative voltage of the whole battery                         |

| $U_{Cell}$ | voltage of the selected accumulator cell (equal to $U_{U2}$ ) |

| $U_{GS}$   | gate-source voltage of a MOSFET                               |

| $U_{Out}$  | output (input) voltage of the full-bridge system              |

| $U_{Set}$  | voltage setpoint value for the closed-loop control            |

| v          | number of measurements                                        |

# TABLE OF CONTENTS

| 1 – I        | NT  | RODU        | <b>CTION</b>                      |

|--------------|-----|-------------|-----------------------------------|

| 1            | .1  | Cell M      | leasurement                       |

|              |     | 1.1.1       | Current                           |

|              |     | 1.1.2       | Temperature                       |

|              |     | 1.1.3       | Voltage                           |

|              |     | 1.1.4       | Need for Balancing                |

| 1            | .2  | Cell B      | alancing Techniques               |

|              |     | 1.2.1       | Cell-to-Heat                      |

|              |     | 1.2.2       | Cell-to/from-Cell                 |

|              |     | 1.2.3       | Cell-to/from-Stack                |

|              |     | 1.2.4       | Cell-to/from-Auxiliary-Source     |

|              |     | 1.2.5       | Technology Comparison             |

| 1            | .3  | Literat     | ture review                       |

|              |     |             |                                   |

| <b>2</b> – C | )R1 | ECTIV       | ${f TE}$                          |

| 3 – T        | EX  | T EXP       | PLANATIONS                        |

| 4 <b>–</b> T | TEC | HNIC        | AL CONCEPT                        |

|              | .1  |             | iew                               |

|              | .2  |             | Multiplexer                       |

|              | .3  |             | C Converter                       |

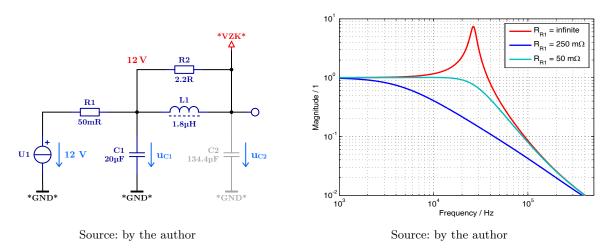

| т            | .0  | 4.3.1       | PI Input Filter   22              |

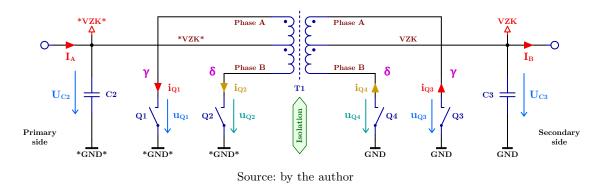

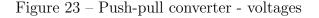

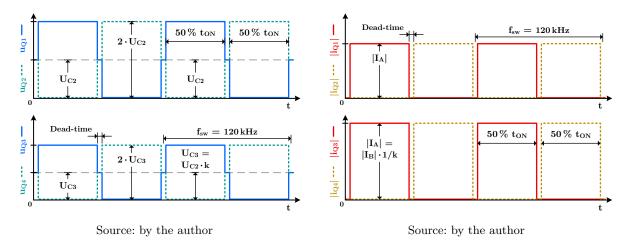

|              |     | 4.3.2       | Push-Pull Converter   24          |

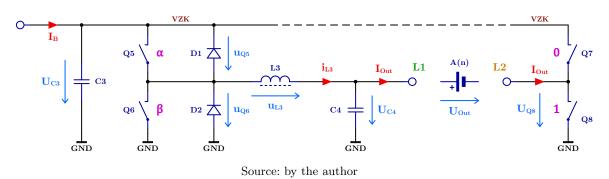

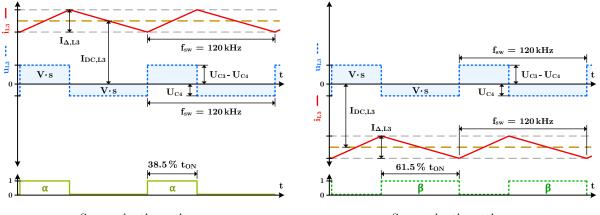

|              |     | 4.3.3       | Full-Bridge Converter   26        |

|              |     | 4.3.4       | Closed-Loop Control Strategy      |

|              |     | 4.0.4       | Closed-Loop Control Strategy      |

| 5 - N        | /IA | <b>FHEM</b> | ATICAL MODEL                      |

| 5            | .1  | Replac      | cement Circuit Modeling           |

|              |     | 5.1.1       | PI Filter Input Stage             |

|              |     | 5.1.2       | Push-Pull Converter Stage    35   |

|              |     | 5.1.3       | Full-Bridge Converter Stage    37 |

| 5            | .2  | State-S     | Space Representation 39           |

|              |     | 5.2.1       | Small-Signal AC Model             |

| 5            | .3  | Transf      | er Function                       |

|              |     | 5.3.1       | Polarity Change                   |

| 6 - DC/ | DC CO   | NVERTER BOARD                               | 47 |

|---------|---------|---------------------------------------------|----|

| 6.1     | Input 1 | Filter                                      | 48 |

|         | 6.1.1   | PI Filter and Safety Fuse                   | 48 |

| 6.2     | Push-F  | Pull Converter System                       | 49 |

|         | 6.2.1   | Bidirectional Push-Pull Converter           | 49 |

|         | 6.2.2   | DC-Link Capacitors                          | 51 |

|         | 6.2.3   | Transformer Construction                    | 52 |

|         | 6.2.4   | Potential Separation                        | 54 |

|         | 6.2.5   | Autostart Circuit                           | 55 |

| 6.3     | Full-Br | idge Converter System                       | 56 |

|         | 6.3.1   | Synchronous Converter                       | 57 |

|         | 6.3.2   | Inductor Construction                       | 58 |

|         | 6.3.3   | High-Low Selection Circuit                  | 60 |

|         | 6.3.4   | Double Charge-Pump                          | 61 |

|         | 6.3.5   | Current-Sink Circuit                        | 62 |

| 6.4     | Measu   | rement System                               | 63 |

|         | 6.4.1   | Cell Voltage Measurement                    | 63 |

|         | 6.4.2   | Cell Current Measurement                    | 65 |

|         | 6.4.3   | DC-Link Voltage and Additional Measurements | 66 |

|         | 6.4.4   | On-Board Temperature Measurement            | 67 |

|         | 6.4.5   | External Temperature Measurement            | 68 |

| 6.5     | Auxilia | ary Power Supplies                          | 71 |

|         | 6.5.1   | 3.3 V and 7.5 V Supplies                    | 71 |

|         | 6.5.2   | 3.3 V Supply with Current Monitoring        | 72 |

|         | 6.5.3   | Switchable 3.0 V Supply                     | 73 |

|         | 6.5.4   | VCC Converter                               | 74 |

|         | 6.5.5   | VDD Converter                               | 75 |

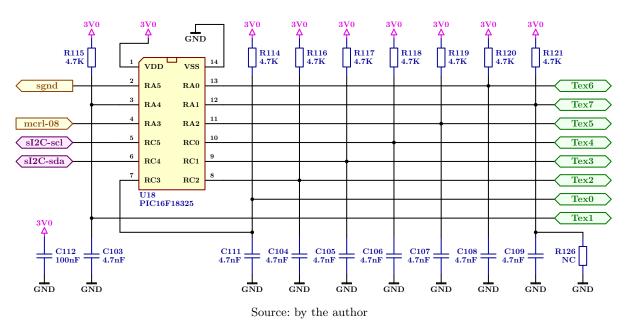

| 6.6     | Digital | Control System                              | 76 |

|         | 6.6.1   | 16-bit Microcontroller                      | 76 |

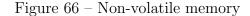

|         | 6.6.2   | Clock Generation and Non-Volatile Memory    | 77 |

|         | 6.6.3   | $I^2C$ Interface                            | 78 |

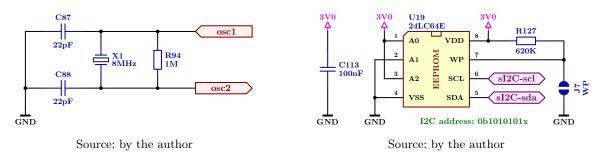

|         | 6.6.4   | EIA-485 Interface                           | 79 |

|         | 6.6.5   | Voltage Reference                           | 79 |

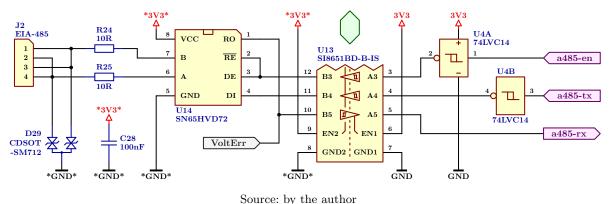

| 6.7     | Power   | and Signal Connectors                       | 83 |

|         | 6.7.1   | +12 V Main Supply Connector                 | 83 |

|         | 6.7.2   | EIA-485 Interface Connector                 | 84 |

|         | 6.7.3   | Board-to-Board Connector                    | 84 |

|         | 6.7.4   | External Temperature Sensor Connector       | 84 |

|         | 6.7.5   | Programming Connector                       | 85 |

| 6.8     | Printe | ed Circuit Board                   |

|---------|--------|------------------------------------|

|         | 6.8.1  | Board Layout                       |

|         | 6.8.2  | Components Assembly Plan           |

| 7 - RES | SULTS  |                                    |

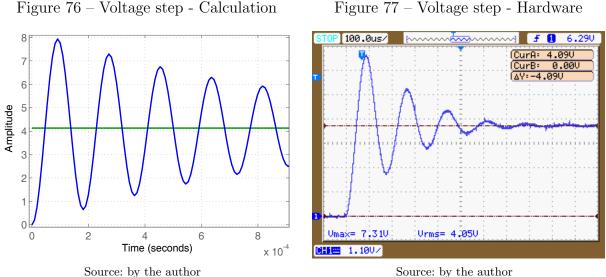

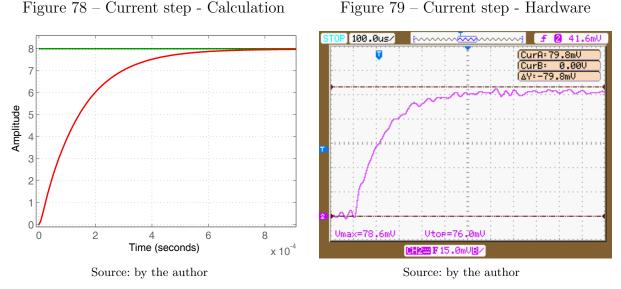

| 7.1     | Step I | Response Analysis                  |

|         | 7.1.1  | Voltage Step                       |

|         | 7.1.2  | Current Step                       |

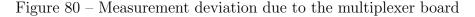

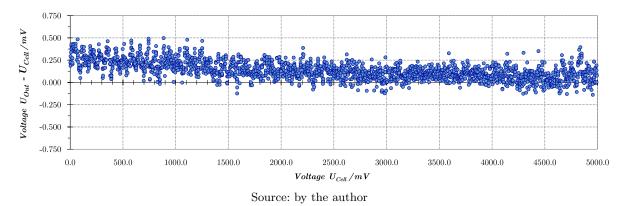

| 7.2     | Cell V | Voltage Measurement Analysis       |

|         | 7.2.1  | Influence of the Multiplexer Board |

|         | 7.2.2  | Without Digital Filtering          |

|         | 7.2.3  | With Digital Filtering             |

| 7.3     | Power  | Conversion Analysis                |

|         | 7.3.1  | Efficiency                         |

|         | 7.3.2  | Power losses                       |

|         | 7.3.3  | Simulation Comparison              |

| 8 – COI | NCLUS  | ION                                |

| 8.1     | Future | e works                            |

| BIBLIC  | OGRAF  | РНҮ 109                            |

## **1 INTRODUCTION**

As a result of the desired and necessary decarbonization of energy generation, the use of renewable energy suppliers is increasing worldwide. Therefore, at distribute locations small power plants produce electrical energy and, depending on requirements and availability, supplies it into the power grid (smart grid). However, the generation of energy from sun, wind, and sea is subject to strong temporal and power fluctuations and typically does not correlate with the energy consumption. For this reason, the need for energy storage solutions is also increasing sharply in order to stabilize the smart grid and deliver energy at the desired time (Roberts; Sandberg, 2011; Molina, 2017; Rodriguez, 2010).

As a chemical energy storage element accumulator cells are used heavily in home batteries and large battery storage power stations (Horiba, 2014; Vartanian; Bentley, 2011; Roberts, 2010). Regardless of this, lithium-ion accumulators are also a key element for electrical vehicles (Winter; Passerini, 2011; Hannan et al., 2018). Therefore, the correct operation of the battery and especially each individual cell is crucial for the reliability and lifespan of the entire system. For this task, every battery requires a highly specialized electronic. This electronic is optimized to supervise and control each cell individually (Xing et al., 2011). For this reason, a high-precision measuring unit determines the voltages of each accumulator cell. The voltage is used to implement an overcharge and deep discharge protection and also indicates the current state of charge (SoC) for each cell. A temperature unit measures the battery temperature at various points and allows to disable or reduce the usable power if under- or over-temperature occurs (Andrea, 2010; ST, 2020; Renesas, 2018). Based on the measurements, a state of safety (SoS) and state of health (SoH) for each accumulator cell can be calculated and tracked over time (Daowd et al., 2011). By knowing every single cell voltage and by measure the charge and discharge currents of the whole battery, also a precise energy monitoring and efficiency calculation can be reached (ST, 2020; Renesas, 2018).

Nevertheless, the most important task of the electronic unit is the cell balancing process (Chang et al., 2014). An imbalance in electrical capacity between all individual cells reduce the capacity of the total battery and its operating time and, consequently, the usable power/energy. Therefore, the electronic must make a charge equalization between the cells (Barsukov, 2009; Wei; Zhu, 2009). This charge equalization can be made by several balancing techniques, with their individual advantages and disadvantages such as passive/active balancing, balancing current and time, efficiency (losses), cell measurement technology (accuracy), number of accumulator cells, etc. (Daowd et al., 2011; Qi; Dah-Chuan Lu, 2014; Omariba; Zhang; Sun, 2019). Regardless of the type of balancing, the electronic must ensure that all cells work in the optimal range at all times (Goldilocks zone - ST (2020)).

#### 1.1 Cell Measurement

To achieve higher nominal voltages for the operation of electrical loads with higher power, single accumulator cells are connected in series. Depending on the application, 350 and more cells are connected to a common string to achieve a total voltage of up to 1600 V (Chang et al., 2014; Wei; Zhu, 2009). In this battery string, each accumulator cell must be operated within strictly defined parameters at all times to reliably avoid damage or destruction of the cell. Even leaving the safe area for a short time should be avoided, as this inevitably reduces the lifespan of the cell and, accordingly, the entire battery system (Korthauer, 2013; Buchmann, 2017).

### 1.1.1 Current

To avoid damage to the accumulator cells, a battery system must not be charged and discharged with excessive currents. The limits for these charging and discharging currents depend on the type of cell used (see cell data sheet information) and the number of accumulator cells connected in parallel. An exact current measurement is therefore necessary to react appropriately when the specified limits are exceeded. In addition, the current measurement (in combination with the cell voltage measurement) is the battery's level indicator. The measurement of the current as well as the time when charging and discharging the battery system provides information on how much electrical charge the cell has absorbed or emitted ( $Q = I \cdot t$ ). Since the current value is accumulated over time, the current measurement unit must work very precisely over a wide range (from milliamperes to hundreds of amperes) and may only have a negligible offset error (Lelie et al., 2018).

Since all accumulator cells are connected in series and the current through all cells are the same, one current measurement per cell string is sufficient to monitor the entire battery. If the string only consists of a few cells (e.g. 10 cells of an electric bike), the current measurement is usually accommodated together with the cell voltage measurement and the balancing electronic on a common printed circuit board (PCB) or in a common housing/module. Batteries with hundreds of cells are frequently divided into modules, with each module having its own balancing electronic. The current measurement itself is carried out only once as a separate unit and inserted at a suitable point on the battery (preferably directly at the positive or negative battery connection). In this case, the current measurement is spatially separated from the balancing electronic and not a part of it (no common PCB).<sup>1</sup> Measurement data (and their timestamp) are collected via a bus system and evaluated centrally in a battery control unit.

<sup>&</sup>lt;sup>1</sup> Depending on the structure of the balancer electronic, it can contain its own internal current measurement to monitor the energy balance within the battery.

#### 1.1.2 Temperature

An essential factor for the safe operation of an accumulator cell is its temperature (Lelie et al., 2018). Apart from special lithium-ion high-temperature cells, the battery can work in an operating range of -60 °C to +60 °C (Ma et al., 2018), depending on the electrolyte used. The optimum operating temperature, where the battery can deliver its full capacity, is around 25 °C. In a cold environment, the mobility of the lithium ions in the electrolyte is restricted and the internal resistance increases sharply (Aris; Shabani, 2017). Hence, the cell can only deliver limited currents at temperatures below 0 °C. At temperatures above 60 °C (depending on the electrolyte used) the electrolyte begins to decompose chemically. It must be considered that the self-heating caused by charging and discharging currents must be added to the ambient temperature and the limit temperature is therefore reached quickly (e.g. 35 °C ambient + 25 °C self-heating = 60 °C).

For this reason, multiple temperature sensors are required to monitor the actual temperature of the battery. In order to reduce the measurement and cabling effort and thus costs, not all accumulator cells are thermally monitored. Temperature sensors are only attached to thermally relevant points on the battery. Also, for cost reasons, mainly thermistors (NTCs or PTCs) and semiconductor diodes are used, with an accuracy of  $\pm 1.0$  °C being achieved. To avoid a short circuit, electrical insulation must be provided between the accumulator cells and the sensors (including measuring lines), as these parts can have different potentials. The temperature measurement circuit is usually carried out together with the balancing electronic and is therefore a part of it. The measured data are processed by the shared digital unit and can be read out via a bus system.

#### 1.1.3 Voltage

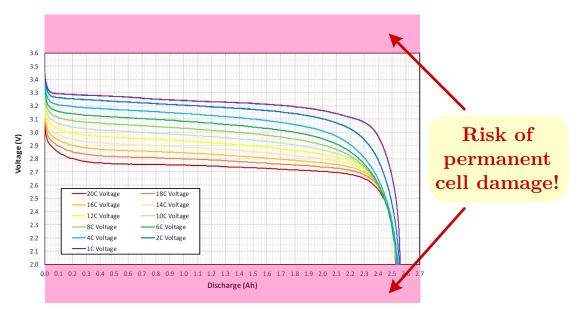

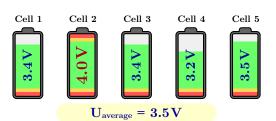

The most important parameter is the cell voltage, which must remain within a maximum and minimum voltage (Andrea, 2010; Buchmann, 2017; Kien; Fowler, 2020). For example, the Figure 1 shows the discharge curve of a LiFePO<sub>4</sub> lithium-ion accumulator cell and its voltage limits. Under 2.00 V undesirable chemical side reactions begin to greatly reduce the capacity and damage the cell. Over 3.60 V internal chemical reactions also begin to destroy the cell. Thereby, the battery cell heats up considerably, which can lead to a thermal runaway and result in an uncontrollable fire in the battery (Kien; Fowler, 2020). For this reason, the safe operating area must never be left.

The values of the voltage limits depends strongly on the materials used in the cell (galvanic respectively electropotential series) and to a lesser extent on the manufacturing process.<sup>2</sup> A good overview of lithium-based battery technologies can be found in Hannan et al. (2018) and Buchmann (2017) while Table 1 shows the typical voltage ranges.

<sup>&</sup>lt;sup>2</sup> Therefore, the voltage of the LiFePO<sub>4</sub> cell in Figure 1 deviates from the maximum achievable cell voltage (Table 1). For the correct voltage limits, please refer to the battery manufacturer's data sheet.

Figure 1 – Discharge curve of a LiFePO<sub>4</sub> cell - example

Source: adapted from LithiumWerks (2019)

Table 1 – Typical cell voltages of different lithium-based accumulator cells

| cell chemistry                     | nominal          | full charge      | full discharge   | minimal          | comment          |

|------------------------------------|------------------|------------------|------------------|------------------|------------------|

| $LiCoO_2$                          | $3.60\mathrm{V}$ | $4.20\mathrm{V}$ | $3.00\mathrm{V}$ | $2.50\mathrm{V}$ | high energy      |

| $LiMn_2O_4$                        | $3.80\mathrm{V}$ | $4.20\mathrm{V}$ | $3.00\mathrm{V}$ | $2.50\mathrm{V}$ | high power       |

| $LiNiMnCoO_2$                      | $3.60\mathrm{V}$ | $4.20\mathrm{V}$ | $3.00\mathrm{V}$ | $2.50\mathrm{V}$ | high capacity    |

| $\rm LiFePO_4$                     | $3.30\mathrm{V}$ | $3.65\mathrm{V}$ | $2.50\mathrm{V}$ | $2.00\mathrm{V}$ | high power, safe |

| $LiNiCoAlO_2$                      | $3.60\mathrm{V}$ | $4.20\mathrm{V}$ | $3.00\mathrm{V}$ | $2.50\mathrm{V}$ | highest capacity |

| ${\rm Li}_4{\rm Ti}_5{\rm O}_{12}$ | $2.40\mathrm{V}$ | $2.85\mathrm{V}$ | $1.80\mathrm{V}$ | $1.50\mathrm{V}$ | long live, safe  |

Source: adapted from Buchmann (2017)

To address every accumulator technology, the balancing electronic must be able to measure the cell voltage, including reserves, in a range of approximately 1.20 V to 4.50 V. To achieve an over- and under-voltage switch-off functionality, it is sufficient to measure this voltage with an accuracy of  $\pm 20 \text{ mV}$ . However, the voltage is important information about the cell capacity and shows the user how much energy actually the cell has. Hence, it is needfully to measure the voltage with an accuracy of  $\pm 1 \text{ mV}$  or better (Lelie et al., 2018). This is specially true for LiFePO<sub>4</sub> accumulators types with the flat voltage curve as seen in Figure 1.<sup>3</sup>

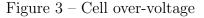

This voltage measurement must be carried out separately for each cell in the string. A common voltage measurement of several accumulator cells or the entire battery stack is not possible, as this does not allow any conclusions to be drawn about the status of an individual cell. Figure 2 illustrates this difficulty, (Omariba; Zhang; Sun, 2019). While the

<sup>&</sup>lt;sup>3</sup> The C-rate (C in Figure 1) indicates the charging or discharging current of an accumulator relating to its total capacity. E.g.: A 4 C discharge current of a 2.5 Ah accumulator cell will be -10 A.

average voltage of the five cells is within the allowable range, cell 2 is out of range, which leads to its destruction (under-voltage). The same effect can be seen in Figure 3, where cell 2 is damaged by over-voltage. The balancing electronic must therefore be especially designed to record all cell voltages reliably and with great accuracy, whereby each voltage to be measured has a different reference potential as a result of the series connection.

Source: adapted from Omariba, Zhang & Sun (2019)

Source: adapted from Omariba, Zhang & Sun (2019)

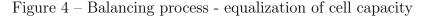

## 1.1.4 Need for Balancing

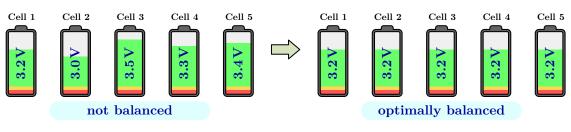

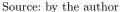

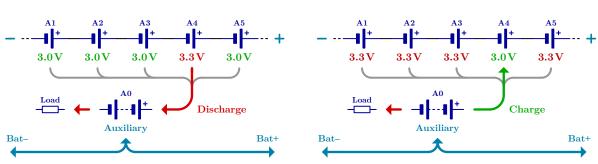

An exact voltage measurement of each battery cell allows a charging or discharging process to be switched off before a cell is damaged, but does not prevent differences in cell capacities and, as a result, the voltages differing from one another. This difference in capacity is caused by production deviations, differences in cell chemistry and different operating conditions (temperature). The small effects accumulate with every charging and discharging process, which over time leads to a significant deviation in capacity and voltage between the individual cells. To compensate for these differences, active intervention by the electronic is necessary. Thereby, electrical energy is redistributed within the battery or across a cell stack (Figure 4).

The importance of cell balancing can be seen in Figure 5 and Figure 6. The charging or discharging process must be stopped when the first cell reaches the voltage limit. Without energy equalization within the battery, the other cells still have energy after the discharge process that cannot be used (Figure 5) and not all cells can be fully charged during the charging process (Figure 6). Depending on the condition and age of the battery, this loss of capacity can considerably limit the operation time of the energy storage system (Qi;

Dah-Chuan Lu, 2014; Omariba; Zhang; Sun, 2019). Balancing the battery is therefore a basic requirement for effective use of all the energy in the battery system, and is used in all devices and systems that use lithium-ion accumulators connected in series.

#### 1.2 Cell Balancing Techniques

Due to the intensive use of lithium-ion accumulator cells for power and energy application such as home batteries, large battery storage power stations and especially electrical cars, intensive research and development in the field of balancing techniques has been carried out in the last decades. In addition, with the further increase in high-capacity electrical energy storage systems, the need for balancing electronics with higher power and efficiency will also increase. There is always a compromise to be made among size, measurement accuracy, power, performance and costs, due to the significant differences between a battery system with ten cells for an electric bike, 100 to 200 cells for an electric car respectively a home storage system, or several 1000 cells for a power plant. For this reason, the balancing technology must be carefully selected, and the electronic must be specifically developed and designed for the battery system used.

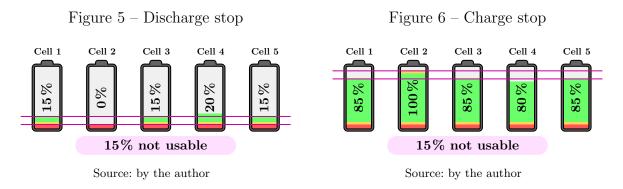

A simple classification of different balancing methods is presented in Figure 7. The stated balancing methods were taken from Daowd et al. (2011), Omariba, Zhang & Sun (2019), whereby these represent only a small selection of possible circuit topologies (Qi; Dah-Chuan Lu, 2014; Caspar; Eiler; Hohmann, 2018). Some balancers given in the literature are modifications or combinations thereof, while others cannot be classified in the above scheme (Tashakor; Farjah; Ghanbari, 2017; Zhang et al., 2019). To better understand the advantages and disadvantages of the balancing circuits, these will be examined in more detail below using the energy transfer concept.

Figure 7 – Cell balancing techniques overview

Source: adapted from Daowd et al. (2011), Omariba, Zhang & Sun (2019)

### 1.2.1 Cell-to-Heat

Passive or cell-to-heat balancing is the simplest and cheapest way to equilibrate a battery system. For this purpose, resistors are connected in parallel to every accumulator cell. Typically, these resistors can be switched electronically to achieve a better control and reduce power losses (Perişoară; Guran; Costache, 2018; Amin et al., 2017). If a cell in the string has more capacity and a higher voltage level than the others, the resistor can be switched on, and the excess energy is converted into heat until all cells have the same voltage (Figure 8).

If a cell has less capacity respectively voltage like in Figure 9, the other cells must be discharge until all cells have the same reduced energy. In both cases, the energy can no longer be used, and the efficiency is therefore zero. If the resistors are not mount on a heat sink, the balancing current (discharge current) is low to keep the heating of the PCB low (typically 30 mA until 300 mA). This leads to long balancing times, especially with large battery capacities. Although this balancing technique is particularly suitable for small battery packs (electric bicycles), this technology is also used in electric vehicles. The simple construction and, in particular, the low costs are preferred properties for using switched-resistor balancing electronics even in large energy storage systems. For this reason, most semiconductor manufacturers offer a wide range of semiconductor chips for cell-to-heat balancing (e.g. BQ76952, BQ76PL455A, MAX17852, LTC6804-1).

#### 1.2.2 Cell-to/from-Cell

Cell-to/from-cell balancing is an active balancing technique where the balancing energy is not lost. Therefore, the excess energy of an accumulator cell is transferred to neighboring cells. These pass on part of the energy to the following cells and so on, until the same energy level respectively voltage is established in all cells. The process is bidirectional, so that accumulator cells with higher voltage are discharged (Figure 10) and cells with lower voltage are charged (Figure 11). The cell-to-cell balancing is disadvantageous if the balancing energy has to be transferred over several cells (in the worst case, from one side of the battery string to the other). In this case, additional conversion losses appear as the energy is shifted from cell to cell and partial losses occur in each stage.

To transfer energy from one cell to another, an energy storage element is necessary. Capacitor-based cell balancers (Ye et al., 2017; Kim et al., 2014) work like a charge pump, where energy is shuttled from one stage to another. The efficiency can be high, if the voltage of the cells are similar. Otherwise, losses in the switches reduces the efficiency drastically (Schlienz, 2007). To deliver equalizing currents in the ampere range, either high switching frequencies with corresponding switching losses or high capacitance values are necessary.<sup>4</sup> If smaller balancing currents are accepted (e.g. 300 mA), efficiency also decreases, since the internal consumption of the electronic accounts for a larger part of the total energy. In Barsukov (2009) an efficiency of 50 % is specified, although this value can be subject to high fluctuations depending on the design.

Inductor-based balancers (Cao et al., 2018; Moghaddam; Van Den Bossche, 2018) can achieve efficiencies of approximately 90%. However, this efficiency is greatly reduced if the energy has to be transferred over several stages. For example, the efficiency drops to 60% if five converter stages are involved. An advantage is that higher equalizing currents are easier to achieve than with capacitor-based balancers, but the costs rise rapidly due to the switching elements and the storage coils have to be scaled with the current. Additionally, the

<sup>&</sup>lt;sup>4</sup> Electrolytic or polymer capacitors should not be used to ensure a long lifespan of the electronic.

electronic require more space. Just like with capacitive balancers, high switching frequencies and complex driver circuitry are required to control each power switch. For example, Texas Instruments Incorporated offers the highly specialized semiconductor bq78PL114, that controls the necessary power MOSFETs. If coil and capacitor are combined, a Cûk, resonant or quasi-resonant balancer can be realized that generate fewer electromagnetic radiation and switching losses (Lee; Cheng, 2005; Ye; Cheng, 2018). As more electronic components are used, the total cost of the electronic also increases.

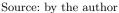

One possibility to greatly reduce the number of capacitors respectively inductors and their costs is to use a multiplexer (switch matrix), made up of individual power switches. In this case, only one single energy storage element is required (Daowd et al., 2011; Yu et al., 2020), which is alternately charged and discharged. Therefore, the power multiplexer switches the capacitor or/and inductor from one cell to another at high frequency (approximately 25 kHz to 250 kHz range). The energy is no longer transferred to neighboring cells, but can take place between any cells. Another advantage besides the reduction of the storage elements is that the cell voltage measuring unit only has to be carried out once (Lee et al., 2015). If the voltages of each accumulator cell is to be measured, the measuring circuit is connected to the multiplexer instead of the storage element (capacitor or/and coil) and the cells are measured one after the other. The disadvantage here is that a corresponding bidirectional power switch for high switching frequencies can only be implemented with great effort and at considerable cost (e.g. PhotoMOS AQZ192 or G3VM-101HR2). Furthermore, a complex regulation and control system is necessary to control the corresponding switches in correct manner.

#### 1.2.3 Cell-to/from-Stack

To overcome the disadvantages of cell-to-cell balancers, greater technical effort is necessary. Cell-to/from-stack balancing bypasses the process of shifting energy over several stages by transferring the excess energy from an accumulator cell to multiple cells at the same time (Figure 12). The opposite way of charging an accumulator cell is also possible and shown in Figure 13. Depending on the requirements, the electronic can be designed so that either the entire battery or a part of the cell string is used. The second allows the battery to be divided into modules or stacks, which increases flexibility and modularity. Thereby, each battery stack requires its own balancing electronic and, which makes things difficult, a charge equalization between the individual battery modules.

For cell-to-stack balancing, transformer-based solution in the form of a DC/DC converter are used. Flyback converters are very common because they are inexpensive and easy to set up. However, any other isolated converter topology, such as forward, push-pull, half-bridge converters etc. (Schlienz, 2007) can also be used. Depending on the design of the electronic, a unidirectional energy transfer (charging or discharging) or a bidirectional

energy flow (charging and discharging) can be realized. The main task is therefore to implement the requirements efficiently and at the lowest possible costs.

The most expensive but also the most flexible solution is to use one DC/DC converter for every cell (Evzelman et al., 2016; Yang; Hu; Tsai, 2020). Therefore, 100 converters would be required for 100 cells connected in series. To reduce the effort and costs at least for the control, several transformers can be controlled by a single power/control unit (Altemose; Hellermann; Mazz, 2011; Arias et al., 2015). Analog Devices Inc offers the LTC3300 semiconductor for this purpose, which uses a flyback topology to address up to six accumulator cells (Preindl, 2018).

Using a single transformer with multiple secondary windings (Bonfiglio; Roessler, 2009; Chen et al., 2020) is even more cost-effective. To select and balance a cell in the battery string, the secondary sides that are connected to the cells must be switchable (Einhorn; Roessler; Fleig, 2011; Park et al., 2014). With the appropriate design of the electronic circuit, the power switches on the primary and secondary side enable a bidirectional operation, so that the accumulator cells can be charged or discharged. In addition to the complex control of the power switches, their triggering (driver circuit) is also a challenge, as the individual switching elements are at different potentials.

The cost, size and efficiency of the transformer can be optimized if only one secondary winding is required. In addition, the control effort is also reduced. To achieve this, the output (respectively input) of the energy converter is switched to the desired accumulator cell, which should be balanced, with the aid of a power multiplexer (Lee et al., 2017; Pham et al., 2016; Nazi; Babaei, 2020). By using a DC/DC converter and a multiplexer the selection process of the cell and the high-frequency switching of the transformer system can be strongly separated from each other (Lin, 2017a; Wu et al., 2019; Kim et al., 2011). This has several advantages. First, the topology of the converter can be freely selected as the multiplexer is not integrated in it. Second, a transformer with only one secondary winding can be used, which reduces space, losses and costs. Third, it is easier to build a bidirectional DC/DC converter that can transfer energy in both directions to charge and discharge the cell. Fourth, the multiplexer and the converter can be developed separately from one another and optimized for efficiency and/or costs. Fifth, a power multiplexer can be implemented more easily if the switching process can be done at low frequency (10 Hz to 1 kHz range). And finally, it is sufficient to implement the cell voltage measuring

unit only once and to scan the individual cell voltages successively with the multiplexer. The main disadvantage for the implementation of a power multiplexer is again the high costs for the bidirectional power switches, since these must be able to block voltages and conduct currents in both directions like a mechanical relay.

The AS8506C battery cell monitor and balancer from ams AG includes a bidirectional switch matrix for addressing up to seven accumulator cells. However, this semiconductor only allows a balancing current up to 100 mA, since all switching elements are combined in one small chip. Texas Instruments Incorporated offers a solution where higher currents are possible. The semiconductors EMB1428Q (switch matrix gate driver) and EMB1499Q (bidirectional DC/DC controller) allows also to balance seven cells. In addition to the control chips, corresponding power MOSFETs are required, which form the actual power multiplexer (e.g. reference design TIDA-00239 and TIDA-00817). Due to the cost of the MOSFETs and especially the control semiconductors (and the dependency on one manufacturer), this solution offers only minor advantages over a multi-winding transformer solution, as described in Einhorn, Roessler & Fleig (2011).

#### 1.2.4 Cell-to/from-Auxiliary-Source

Cell-to/from-auxiliary-source balancing (not shown on Figure 7) is very similar to the cell-to-stack balancing. But instead of using the entire battery respectively a battery module as a source (or sink) for energy transfer, an auxiliary supply is used (Figure 14 and Figure 15). This supply has usually a low voltage of, for example, 12 V and must be able to deliver and absorb electrical energy (depending on the balancing circuit). Therefore, a battery such as that founds in vehicles is typically used for this source. In electric cars, this "starter battery" supplies numerous of low-power consumers such as board computer, entertainment, lighting, ventilation, etc. In the case of a home battery or a large battery storage power station, this supplies cooling devices, ambient sensors and display systems, etc. An example for a balancer circuit with a +12 V auxiliary supply input are the reference designs TIDA-00239 and TIDA-00817 from Texas Instruments Incorporated.

Figure 15 – Auxiliary source to cell

Source: by the author

Source: by the author

The auxiliary power supply is typically connected to the high-voltage battery via an own high-voltage, bidirectional DC/DC converter and allows energy to be exchanged between the two battery systems. Therefore, the energy transfer between a cell and the entire battery always takes place via two steps (high-voltage DC/DC converter and balancer electronic). Although this reduces the efficiency slightly (approximately -2.5%), it enables greater flexibility and modularity of the individual electronic units. One advantage is that the high-voltage, bidirectional DC/DC converter can be optimally designed for the voltage range and the power requirements of the high and low voltage batteries, whereby efficiencies of up to 97% can be achieved. For the balancing electronic, a universal voltage input of around 12.00 V (approximately 8.00 V to 16.00 V) is sufficient and does not have to be adapted to the battery system every time. Another advantage is that balancing energy can be exchanged directly between battery modules or stacks thanks to the +12 V supply bus (Evzelman et al., 2016; Preindl, 2018). Hence, an extra balancing unit between the modules is not necessary.

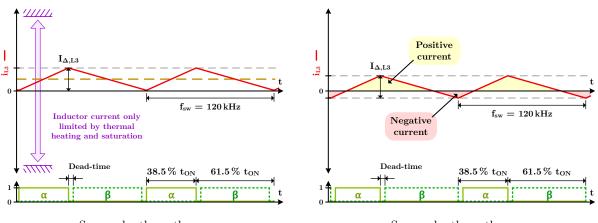

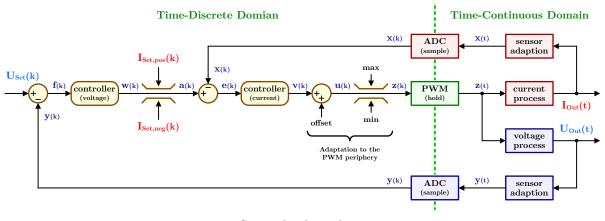

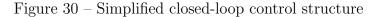

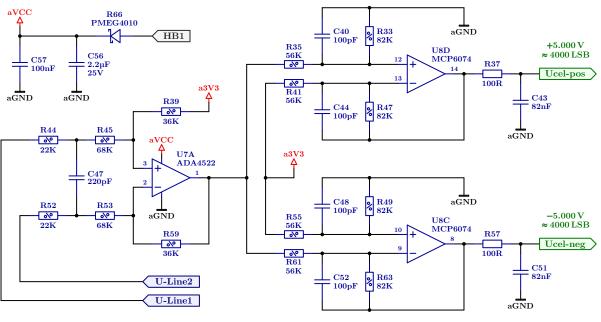

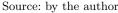

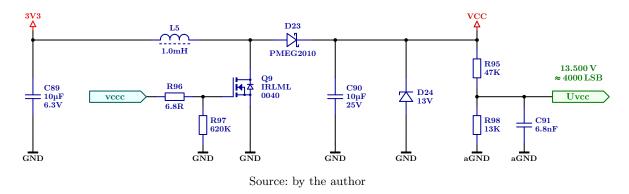

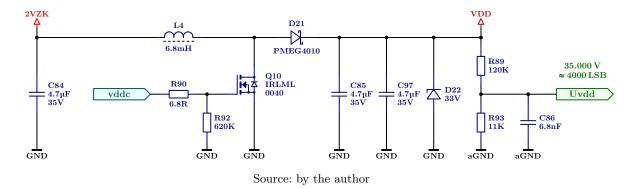

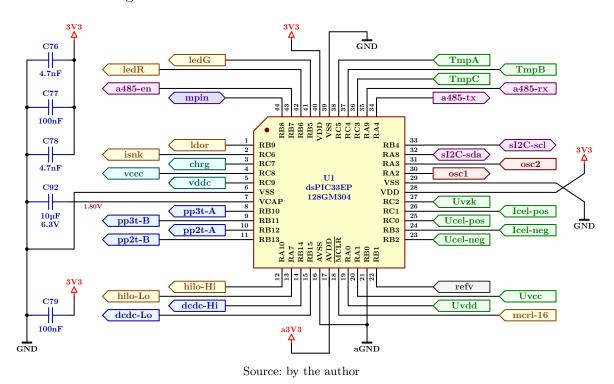

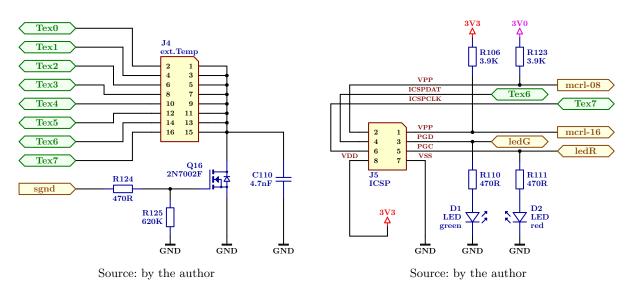

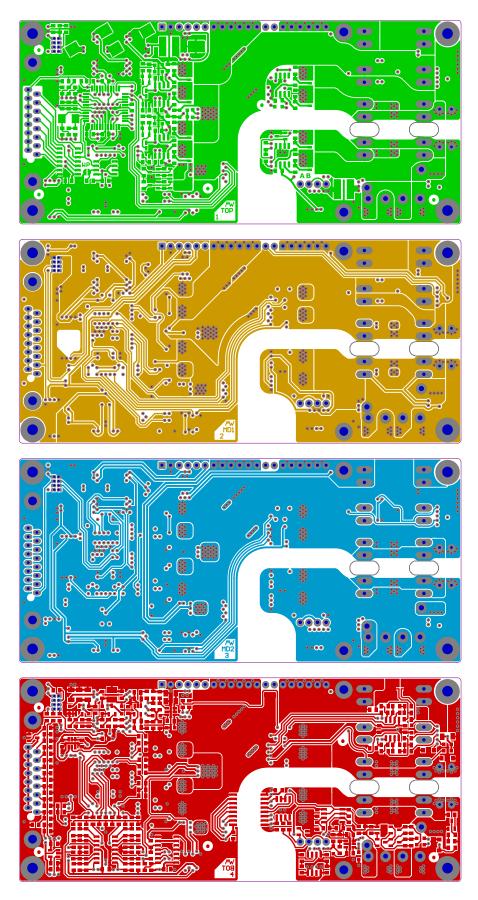

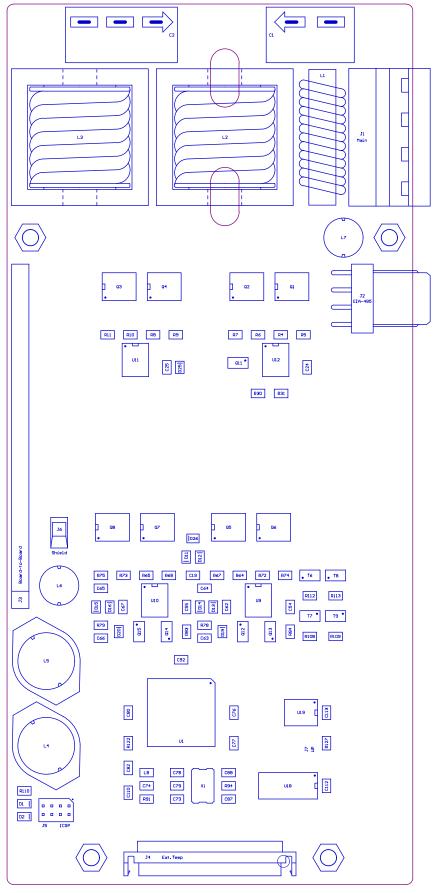

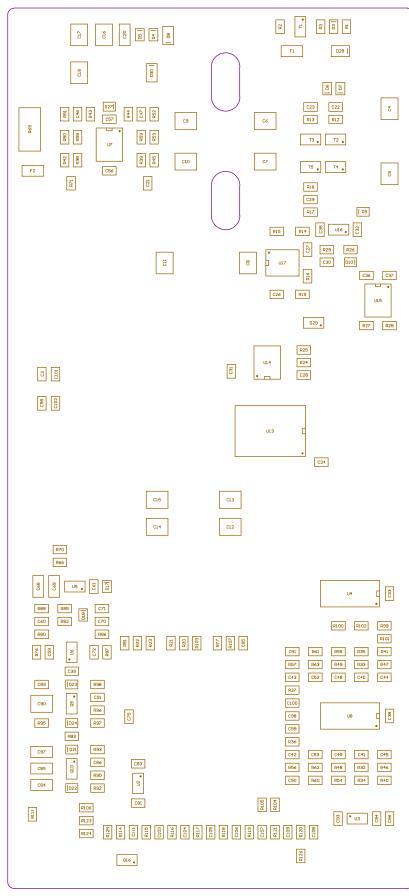

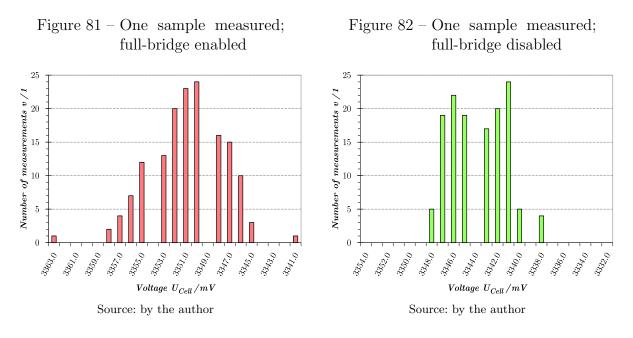

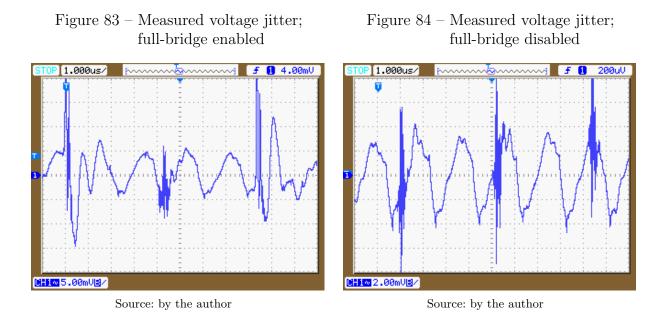

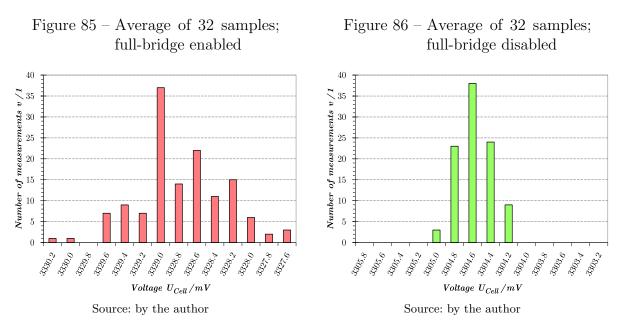

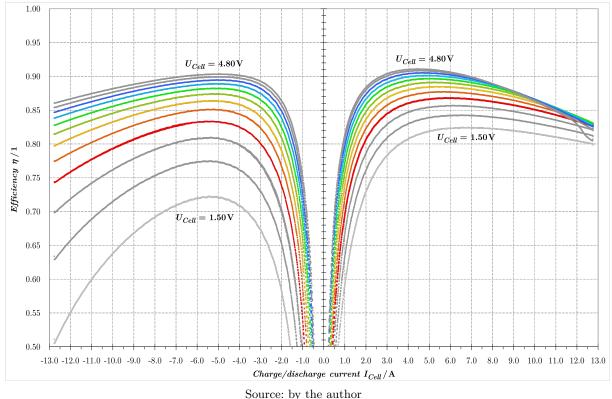

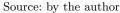

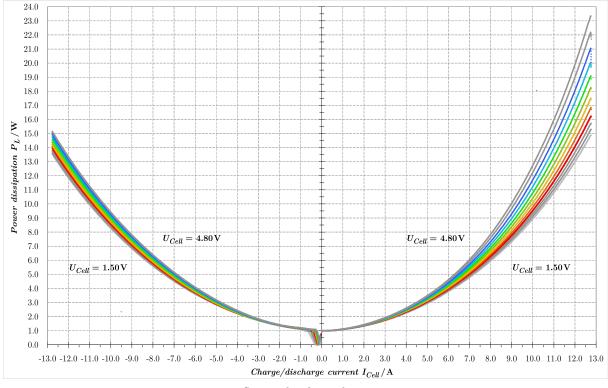

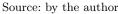

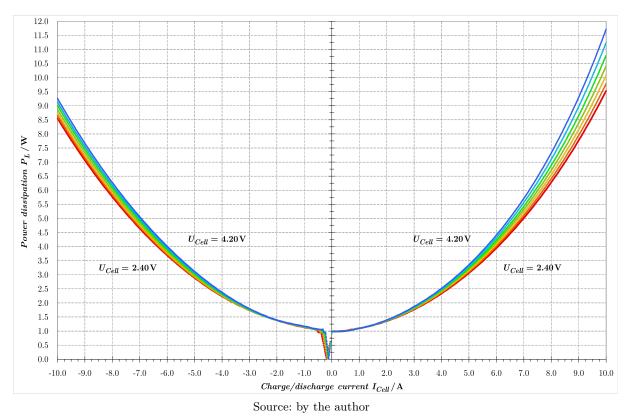

#### 1.2.5 Technology Comparison