# Desenvolvimento de monografia

# Revisão Bibliográfica: Erros Causados por Raios Cósmicos em Dispositivos Eletrônicos

Prof. Dr. Helder Galeti

Professor(es) Responsável(is)

Autora

Isabella Moreira de Sousa Paulo

RA: 728294

Isabella Moreira de Sousa Paulo

Revisão Bibliográfica: Erros Causados por Raios Cósmicos em Dispositivos Eletrônicos

Monografia apresentada ao Programa de Graduação em Engenharia Elétrica da Universidade Federal de São Carlos para obtenção do título de bacharel em engenharia elétrica.

Orientador: Helder Galeti

São Carlos - SP 2023

# Agradecimentos

Agradeço à minha mãe Dirce Moreira de Sousa e a minha irmã pelo incentivo e suporte durante todos os momentos.

Agradeço meu orientador Helder Galeti que apesar da intensa rotina de sua vida acadêmica aceitou me orientar nesta monografia. As suas valiosas instruções e suporte para a pesquisa fizeram toda a diferença.

Também agradeço à todos os meus colegas de curso, pelas horas de estudo, oportunidade do convívio e pela companhia durante estes anos.

## Resumo

Os raios cósmicos, provenientes do espaço, penetram em dispositivos eletrônicos de modo a alterar diversas características como funcionamento, desempenho e vida útil. Essas partículas são compostas por partículas atômicas, constituídas de prótons e nêutrons, ultra energéticos que viajam em altas velocidades em direção à superfície terrestre e que em razão de sua alta energia podem penetrar facilmente componentes elétricos e eletrônicos. Esses efeitos são encontrados principalmente em locais com maiores altitudes e latitudes, porém podem ser observados ao nível do mar em menor escala. Com o avanço da microeletrônica, o choque dessas partículas com componentes eletrônicos gera uma carga elétrica parasita que prejudica o funcionamento de diversos dispositivos, desde memórias, componentes eletrônicos de potência até relés e supercomputadores. Assim, a proposta deste trabalho é relatar e dar compreensão sobre a influência de cósmicos no funcionamento de componentes elétricos e eletrônicos de forma aprofundada, através de uma revisão de dados disponíveis na literatura. Pretende-se avaliar o impacto no funcionamento de componentes eletrônicos, dispositivos elétricos e no aprimoramento de novas tecnologias.

Palavras-chave: Circuitos Eletrônicos, Dispositivos Elétricos, Raios Cósmicos

# Abstract

Cosmic rays, coming from outer space, can penetrate eletronic devices in order to change several characteristics such as functioning, performance and useful life. These particles are composed of an atomic nuclei, made up of ultra energetic protons and neutrons, that travel at high speeds towards the earth's surface, due to their high energy they can easily penetrate electrical and electronic components. These effects are easily found at higher altitudes, but can be observed at sea level on a smaller scale. With the advancement of microelectronics, the collision of these particles with electronic components generates a parasitic electrical charge that harms the operation of several devices, from memories, power electronics to relays and supercomputers. Thus, the purpose of this work is to report and provide an in-depth understanding of the influence of cosmic rays on the operation of electrical and electronic components, through a review of data available in the literature. The aim is to assess the impact on the operation of electronic components, electrical devices, and the advancement of new technologies.

Keywords: Eletronic Circuits, Electrical Devices, Cosmic Rays

# Lista de Figuras

| 1  | Esquema do modelo padrão de física das partículas                                           |    |  |  |  |

|----|---------------------------------------------------------------------------------------------|----|--|--|--|

| 2  | Fluxograma esquemático representando toda a estrutura de um chuveiro                        |    |  |  |  |

|    | atmosférico                                                                                 |    |  |  |  |

| 3  | Ilustração do modelo de Heitler, onde temos um elétron realizando suces-                    |    |  |  |  |

|    | sivos desdobramentos a cada distância $d$                                                   | 16 |  |  |  |

| 4  | Ilustração do modelo de Heilter-Matthews, onde temos um raio cósmico                        |    |  |  |  |

|    | realizando sua primeira interação à profundidade de $\chi^0$ e produzindo píons             |    |  |  |  |

|    | carregados, $\pi^{\pm}$ , e píons neutros, $\pi^{0}$                                        | 17 |  |  |  |

| 5  | Ilustração do modelo de Heilter-Matthews, onde temos um raio cósmico                        |    |  |  |  |

|    | realizando sua primeira interação à profundidade de $\chi^0$ e produzindo píons             |    |  |  |  |

|    | carregados (denotados por $\pi^{\pm}$ ) e píons neutros (denotados por $\pi^0$ )            | 18 |  |  |  |

| 6  | Réplica do primeiro transistor desenvolvido em 1947                                         | 21 |  |  |  |

| 7  | Linha do tempo de evolução do transistor                                                    | 23 |  |  |  |

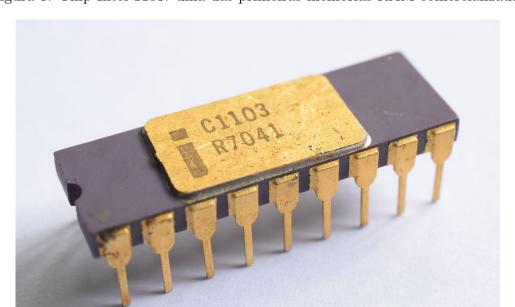

| 8  | Chip Intel 1103: uma das primeiras memórias RAM comercializadas                             | 25 |  |  |  |

| 9  | O espectro de energia de raios cósmicos de ferro, hidrogênio e hélio                        | 28 |  |  |  |

| 10 | O espectro de energia diferencial de hidrogênio acumulado para as explosões                 |    |  |  |  |

|    | solares de 4 de agosto 1972 a 10 de agosto de 1972. Isso é comparado com                    |    |  |  |  |

|    | o espectros de hidrogênio de raios cósmicos galácticos acumulados por uma                   |    |  |  |  |

|    | semana no máximo solar e mínimo respectivamente                                             | 29 |  |  |  |

| 11 | Exemplo de três trajetórias de partículas                                                   | 35 |  |  |  |

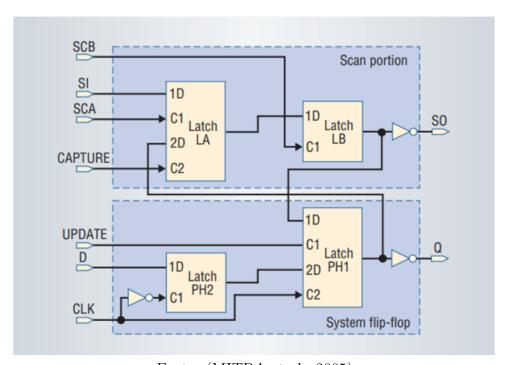

| 12 | Design de célula de varredura do microprocessador. O sistema tem dois                       |    |  |  |  |

|    | modos de operação: sistema normal de operação e teste                                       | 38 |  |  |  |

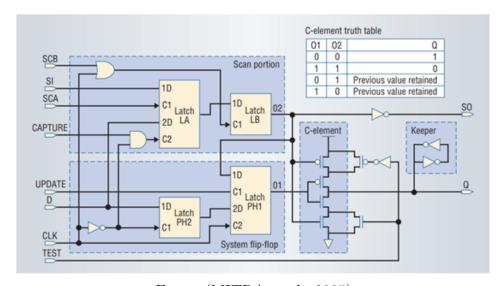

| 13 | Reutilização da varredura. Flip-flop bloqueador de erro suave com um                        |    |  |  |  |

|    | elemento C. Reutilizar o flip-flop de varredura reduz o impacto de erros                    |    |  |  |  |

|    | suaves que afetam os latches em até 20 vezes                                                | 39 |  |  |  |

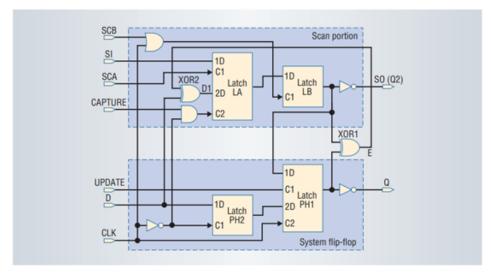

| 14 | Design da célula de varredura e captura de erro.                                            | 40 |  |  |  |

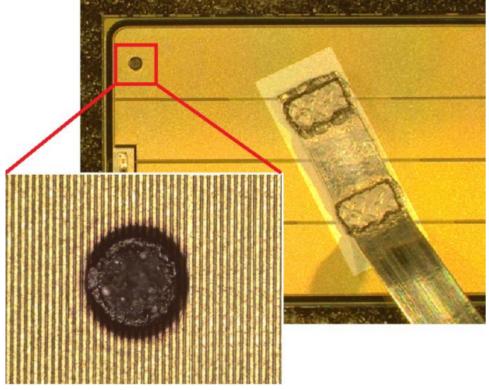

| 15 | Exemplo de queima causada no SEB                                                            | 42 |  |  |  |

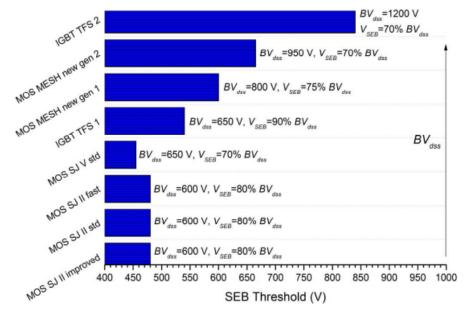

| 16 | Tensão mínima em que os dispositvos em teste falharam                                       | 43 |  |  |  |

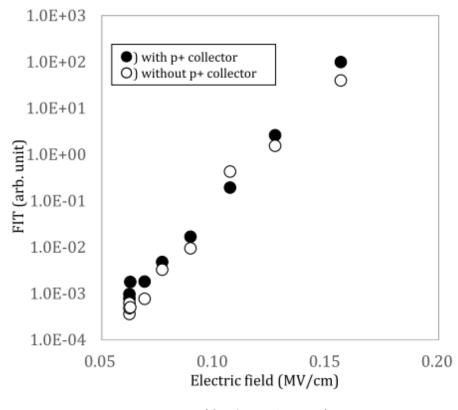

| 17 | Dependência do campo elétrico no FIT medido                                                 | 46 |  |  |  |

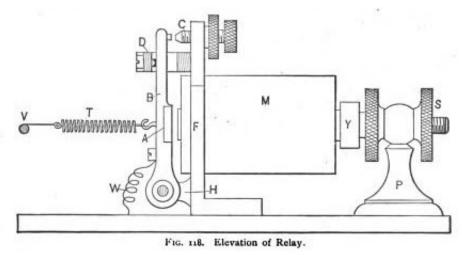

| 18 | Diagrama de um relé típico do final do século XIX. A mola (T) mantém o                      |    |  |  |  |

|    | braço (B) afastado do contato (C). Quando o eletroímã (M) é ativado, ele                    |    |  |  |  |

|    | supera a força da mola e fecha o circuito entre o fi<br>o ${\bf W}$ e o contato $({\bf C})$ | 48 |  |  |  |

| 19 | Evolução dos Relés de Proteção                                                              | 50 |  |  |  |

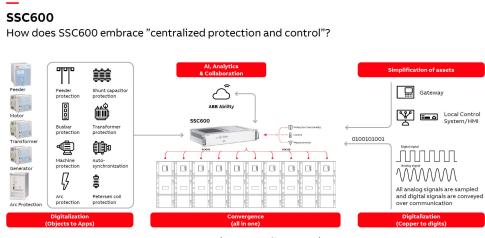

| 20 | Exemplo de utilização do SSC600                                                             | 51 |  |  |  |

| 21 | Exemplo de aplicação de conformal coat numa PCB                                             | 54 |  |  |  |

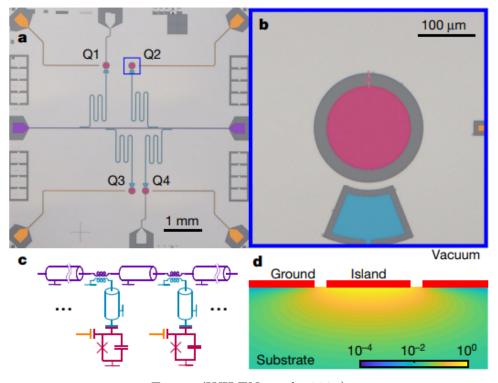

Layout e resposta de carga do chip. a, Micrografia óptica do chip multiqubit. Quatro qubits transmon sensíveis à carga (Q1-Q4, magenta) estão acoplados a ressonadores de leitura local (ciano) e linhas de portão de carga (laranja). Os ressonadores de leitura estão acoplados a uma linha de alimentação comum (roxa). A imagem é uma composição costurada (consulte Informações Suplementares). b, Vista ampliada de um único qubit. c, Diagrama de circuito do chip. A codificação de cores corresponde à coloração falsa em a e b. d, Simulação da carga induzida na ilha do qubit a partir de uma carga pontual unitária em várias localizações no substrato de silício.

56

Lista de Figuras 8

# Lista de Abreviaturas e Siglas

CCD Dispositivo de Carga Acoplada

CIA Corrente Induzida por Avalanche

CLK Clock

CMOS Complementary metal-oxide-semiconductor

CREME Cosmic Ray Effects on Micro-Eletronics

DRAM Dynamic Random Access Memory

FPGA Field-programmable Gate Array

GCR Galatic Cosmic Rays

GTO Gate Turn-off Thyristor

IGBT Insulated Gate Bipolar Thyristor

LET Linear Energy Transfer

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

PCB Placa de Circuito Impresso

RAM Random Access Memory

SCR Solar Cosmic Rays

SEB Single-event Burnout

SEF Single Error Filtering

SER Soft Error Rate

SEU Single Event Upset

TMR Redundância Modular Triplicada

VLSI Very Large Scale of Integration

# Sumário

| <b>1.</b> | $\mathbf{Intr}$ | odução                   |                                                                        | 10 |  |  |

|-----------|-----------------|--------------------------|------------------------------------------------------------------------|----|--|--|

|           | 1.1.            | Motiva                   | ação                                                                   | 10 |  |  |

|           | 1.2.            | Ráios                    | Cósmicos                                                               | 10 |  |  |

|           | 1.3.            | . Partículas Subatômicas |                                                                        |    |  |  |

|           | 1.4.            | 4. Cascatas              |                                                                        |    |  |  |

|           |                 | 1.4.1.                   | EAS - Extensive Air Shower                                             | 15 |  |  |

|           |                 | 1.4.2.                   | Cascata Eletromagnética                                                | 16 |  |  |

|           |                 | 1.4.3.                   | Cascata Hadrônica                                                      | 17 |  |  |

|           | 1.5.            | Interac                  | ção de raios cósmicos com semicondutores                               | 18 |  |  |

| 2.        | Desenvolvimento |                          |                                                                        |    |  |  |

|           | 2.1.            | Primei                   | ira Geração de Pesquisas                                               | 19 |  |  |

|           |                 | 2.1.1.                   | Memória RAM                                                            | 19 |  |  |

|           |                 | 2.1.2.                   | Erros suaves em memórias RAM                                           | 21 |  |  |

|           |                 | 2.1.3.                   | Correção de erros suaves na primeira geração                           | 30 |  |  |

|           |                 | 2.1.4.                   | O modelo CREME                                                         | 31 |  |  |

|           | 2.2.            | Segund                   | da Geração de Pesquisas                                                | 31 |  |  |

|           |                 | 2.2.1.                   | Falhas em dispositivos de potência                                     | 32 |  |  |

|           |                 | 2.2.2.                   | Dispositivos CMOS e MOSFET                                             | 33 |  |  |

|           |                 | 2.2.3.                   | Sistema de varredura de células                                        | 38 |  |  |

|           |                 | 2.2.4.                   | Pesquisas recentes em Dispositvos de Potência                          | 41 |  |  |

|           | 2.3.            | Sistem                   | as de proteção                                                         | 47 |  |  |

|           |                 | 2.3.1.                   | Relés e IEDs                                                           | 47 |  |  |

|           |                 | 2.3.2.                   | Como é feito o processo de fabricação de dispositivos microprocessados | 51 |  |  |

|           |                 | 2.3.3.                   | Proteção de PCBs com Conformal Coating                                 | 53 |  |  |

|           | 2.4.            | Tendê                    | ncias de Pesquisas Futuras                                             | 55 |  |  |

| 3.        | Con             | clusão                   |                                                                        | 57 |  |  |

| Re        | Referências     |                          |                                                                        |    |  |  |

# 1. Introdução

## 1.1. Motivação

Com o grande avanço tecnológico que vemos nos últimos anos cada vez mais dispositivos eletrônicos são utilizados em tarefas, funcionalidades e comunicação contidianas pela sociedade como um todo. Esses equipamentos elétricos e eletrônicos são constituidos muitas vezes de microeletrônicos que tem seu tamanho cada vez mais reduzido e que realizam as funções de um computador com cada vez mais eficiência.

De maneira direta ou indereta esses dispositivos estão presentes em nossas vidas, seja no seu smartphone, computador pessoal, na subestação que fornece energia para sua casa e para as indústrias funcionarem ou hospitais funcionarem. Entretanto caso esses dispositivos não funcionem de maneira correta podemos ter diversos prejuízos.

Uma das fontes de erros em microeletrônicos são raios cósmicos. No Brasil não temos tantos estudos voltados para esses tipos de interferência causadas por raios cósmicos em eletrônicos, provavelmente por conta da localização geográfica do país. Em países com maior altitude, em relação ao nível do mar, bem como mais próximos aos pólos (maiores latitudes), os componentes elétricos tendem a ser mais afetados por essa radiação. Porém se desejamos fabricar e exportar dispositivos eletrônicos eficientes é interessante conhecer um pouco mais como podemos evitar que os dispositivos sejam afetados.

Com o objetivo de atrair atenção para o tema no Brasil, o presente trabalho reune uma revisão organizada de diversos estudos realizados sobre os efeitos da radiação cósmica em dispositivos eletrônicos e meios de se contornar e evitar falhas relacionadas a raios cósmicos.

#### 1.2. Ráios Cósmicos

Podemos considerar que os estudos envolvendo partículas cósmicas tiveram início no século XVIII com Charles Augustin de Coulomb (1736-1806) quando realizou um experimento que resultou na hipótese da existência da condutividade intrínseca do ar. Seu experimento pode ser corroborado mais tarde pelos físicos Michel Faraday (1791-1867) e William Crookes (1832-1919) que observaram que a velocidade de descarga era proporcional à pressão atmosférica. Em 1986 Henri Becquerel (1852-1908) realizou um experimento que deu o nome de raios ionizantes aos raios emitidos por sais de urânio que conseguiam aumentar a condutividade do ar, em outras palavras, eram capazes de retirar elétrons dos átomos dando origem a íons livres (BANDEIRA, 2018).

Entre 1909 e 1911, Domenico Pacini realizou experimentos no Golfo de Gênova para buscar medidas da condutividade do ar. Ele realizou medições com um eletrômetro em uma caixa de cobre para conseguir realizar testes no mar a 3m de profundidade e a 300m da costa, comparando as taxas de descarga medidas com o aparelho na superfície e

submerso pôde observar um decréscimo de 20% quando mesmo estava embaixo da água. Com isso ele conseguiu comprovar a existência de uma radiação altamente penetrante e não proveniente da superfície terrestre ou atmosfera, uma vez que a água absorveria essa radiação (BANDEIRA, 2018).

Em 1911 Viktor Franz Hess (1883-1964) começou a realizar experiências com balões. Os experimentos foram realizados durante a noite e de dia com um eclipse total, assim era possível desconsiderar o Sol como fonte direta de radiação. Munido de um eletroscópio e um detector de ionização o balão foi solto até a altura de 5350m onde se constatou um aumento evidente dos efeitos ionizantes sem influência de fontes terrestres e atmosféricas. Deixando claro que a fonte dessa radiação era extraterrestre(BANDEIRA, 2018).

A partir da comprovação que os raios vinham de fora da Terra diversos estudos começaram a ser desenvolvidos para descobrir sua origem. Porém apenas após uma década dos experimentos de Pacini e Hess foi finalmente adotado o termo radiação cósmica(BANDEIRA, 2018).

Pode-se subdividir os raios nas quatro categorias abaixo (ZIEGLER, 1996):

- ❖ Raios Cósmicos Primários: partículas galácticas que penetram o sistema solar e podem chegar à terra;

- \* Raios Cósmicos Solares: partículas no vento solar que é originada no Sol;

- ❖ Raios Cósmicos Secundários: partículas produzidas na atmosfera terrestre a partir de raios cósmicos primários;

- ❖ Raios Cósmicos Terrestres: partículas que atingem a Terra (solo terrestre). Esses raios representam menos de 1% das partículas primárias e geralmente estão entre a terceira e sétima geração de partículas formadas nas cascatas, que será apresentada nas seções seguintes.

Mesmo a determinação da origem dos raios cósmicos por métodos diretos sendo impossível devido a trajetória aleatória que ocorre por conta das interações com campos magnéticos durante sua trajetória do espaço até a Terra é possível apontar algumas fontes (BANDEIRA, 2018). Através de métodos indiretos foi comprovado que o Sol é uma das fontes desses raios, este tem uma energia na faixa de 10<sup>9</sup>eV e podem seu raios podem ser abreviados como SCR (Solar Cosmic Rays)(ZIEGLER, 1996).

As partículas solares têm uma energia inferior se comparada a outras fontes. E o ciclo solar influência na quantidade de partículas que conseguem atingir a Terra. Além disso, durante o ciclo temos dois períodos que são chamados de período de atividade mínima e período de atividade máxima do ciclo solar e ocorrem em um intervalo de 11 anos(ZIEGLER, 1996).

Durante o período de atividade mínima quase não há partículas com energia suficiente para atingir o nível do mar. Já durante o período de atividade máxima o número de

partículas que atingem a atmosfera aumenta mil vezes sendo maior que o fluxo de raios cósmicos provenientes de outras galáxias, esses tendo energia suficiente para chegar ao nível do mar(ZIEGLER, 1996).

Outras fontes de raios cósmicos são estudadas observando o processo de aceleração natural das partículas. Uma teoria é que o processo de aceleração de partículas por sua interação com estrelas o gás interestelar ao penetrar a helioesfera ocorre através da fotoionização ou trocas com o material presente no vento solar. Hoje é considerado que raios cósmicos com espectro de energia entre  $10^9 {\rm eV}$  e  $10^{16} {\rm eV}$  são acelerados por remanescentes ordinários de supernovas(BANDEIRA, 2018).

Acredita-se que os raios cósmicos com energias superiores a  $10^{18}$  eV que atingem a Terra são produzidos fora de nossa galáxia a Via Láctea. No entanto, ainda não existem conhecimentos suficientes acerca das fontes exatas dos raios cósmicos ultra energéticos, porém alguns objetos astrofísicos são apontados como possíveis fontes: galáxias com núcleos ativos, estrelas de nêutrons e explosões de raios  $\gamma$  (BANDEIRA, 2018).

### 1.3. Partículas Subatômicas

Como visto anteriormente os raios cósmicos são formados de diversas partículas provenientes do espaço e que interagem com partículas terrestres. Entre elas temos diversas partículas subatômicas que serão descritas a seguir. Elas se relacionam de diferentes maneiras com os elementos e a atmosfera terrestre.

O Modelo Padrão das partículas elementares

que são ventadeiramente elementares, não têm estrutura internas

Léptons

Quarks

Hádrons

Léptons

Quarks

Hádrons

Eletronagnética

Forte

Fraca

Gravitacional

A devida à d

Figura 1: Esquema do modelo padrão de física das partículas

A física de partículas é uma área da física que estuda as partículas fundamentais que

compõem o universo e as interações entre elas. Essas partículas são as unidades básicas da matéria e da energia. Alguns conceitos fundamentais que são abordados na física de partículas que podem ajudar a compreender a relação entre as partículas presentes no raios são:

- ❖ Partículas Elementares: São as partículas que não possuem estrutura interna conhecida, ou seja, são consideradas "pontuais" na teoria. Exemplos incluem léptons (como elétrons e neutrinos) e quarks (que compõem prótons e nêutrons).

- ❖ Interações Fundamentais: Existem quatro interações fundamentais conhecidas na natureza: força gravitacional, força eletromagnética, força fraca e força forte. A física de partículas estuda como essas interações funcionam em nível subatômico.

- ❖ Modelo Padrão: É a teoria que descreve as partículas elementares conhecidas e as forças que agem entre elas. Ele inclui léptons, quarks e as partículas mediadoras das interações fundamentais.

- ❖ Aceleradores de Partículas: São instrumentos usados para estudar partículas em altas energias, acelerando-as a velocidades próximas à da luz e colidindo-as entre si. Exemplos famosos incluem o Grande Colisor de Hádrons (LHC) no CERN.

- ❖ Bósons de Higgs: É uma partícula elemental prevista pelo Modelo Padrão, descoberta em 2012 no LHC. O bóson de Higgs é responsável pela atribuição de massa às outras partículas elementares.

- ❖ Física Além do Modelo Padrão: Apesar de ser uma teoria poderosa, o Modelo Padrão tem limitações e não consegue explicar fenômenos como a matéria escura e a energia escura. Portanto, os físicos de partículas também procuram por evidências de novas partículas e novas teorias que possam estender ou substituir o Modelo Padrão.

O núcleo atômico é composto de prótons e nêutrons, porém existem forças de coesão nuclear como múons e píons que mantém as cargas "juntas" e estáveis, uma vez que os prótons têm carga positiva e os neutros podem ter carga positiva e negativa. O nucleon é um próton ou nêutron presente no núcleo atômico e é constituído por três quarks com uma interação entre eles que resulta da ação da força nuclear forte (THOMAS; WEISE, 2001).

Múon (Muão) é uma partícula que tem carga elétrica -1 semelhante ao elétron, porém sua massa é de  $105,7 MeV/c^2$ , mais que o dobro da massa de elétron. Junto ao tau e os neutrinos é considerado um lépton. Tem decaimento rápido, porém não são fortemente acelerados quando em contato com campos eletromagnéticos e não emitem tanta radiação. Isso permite que o múon penetre com mais profundidade do que os elétrons (CONNECTION, 2023).

Na física das partículas temos alguns dois tipos de partículas elementares que formam a matéria, são elas o quark e o lépton. O quark se combina de maneira a formar partículas compostas que são chamadas de hádrons. E o Píon (ou méson pi) é uma partícula subatômica composta por um quark e um antiquark, quando carregados decaem em múon e neutrino de múon e se neutros decaem em raios gama. Naturalmente são produzidos quando prótons de alta energia dos raios cósmicos e outros componentes hadrônicos presentes nos raios interagem com a atmosfera terrestre. Através da detecção da origem de raios gamas foi possível identificar que píons são produzidos abundantemente em supernovas (LATTES et al., 1947).

Neutrino é uma partícula subatômica hadrônica sem carga com massa de  $10^{-21}g$  e sua interação forte se extende apenas a  $10^{-13}cm$  da partícula. Ele pode ser um neutrino do eletrón que participa da mesmas interações que um elétron, neutrino de múon e neutrino de tau e assim como a anterior só participa de interações que as partículas de múon e tau participam. Pode-se estimar a probabilidade de um neutrino energético interagir com um circuito de silicío. Um núcleo de silício tem massa atômica de 28 com 14 protóns e 14 neutrons, assim o raio do núcleo é de aproximadamente  $4x10^{-13}cm$  e uma área transversal de  $5x10^{-25}cm^2$  e nessa área acontece uma absorção total que podemos chamar de Black Wall com área de  $2x10^{24} \acute{a}tomos/cm^2$  e a densidade do sílicio de  $5x10^{22} atomos/cm^3$ . Com isso o comprimento da absorção do silício é de 40cm, assim a probabilidade de um neutrino interagir com o silício é de 1 em 40000 (ZIEGLER, 1996).

Fóton é uma partícula elementar que se propaga na na forma de uma onda eletromagnética e interage como uma partícula com energia e momentum. São produzidos por átomos quando um elétron da camada de valência se move de um orbital para um outro orbital de energia diferente ou através de um decaimento nuclear (SILAS, 2023).

Positron é uma partícula elementar (com carga contrária ao eletron +1 e spin  $\frac{1}{2}$  e mesma massa do eletron, por isso também é chamado de antielétron) que é formada após o decaimento radioativo de uma emissão beta ou através de interação de fótons de alta energia com a matéria. Quando um pósitron interage com um eletron a massa de ambos é transformada em fótons ou outras partículas (ANTIMATÉRIA, 2018).

#### 1.4. Cascatas

Após seu trajeto no espaço o raio cósmico pode penetrar a Terra, tanto em sua atmosfera quanto em sua superfície, formando um espectro durante esse processo. Ao adentrar a atmosfera, o raio cósmico colide com núcleos presentes no ar gerando decaimentos e ionizações e até mesmo criando algumas partículas.(BANDEIRA, 2018). Antes de atingir o nível do mar partículas como núcleons e píons realizam diversas colisões. Como a interação com o ambiente é muito forte, quase nenhuma partícula primária chega a atingir o mar ou solo. Assim, são formadas cascatas de partículas de diversas interações

até que se chegue ao nível do mar. Essas partículas são em sua maioria píons, múons, núcleons, elétrons, e fótons (ZIEGLER, 1996).

#### 1.4.1. EAS - Extensive Air Shower

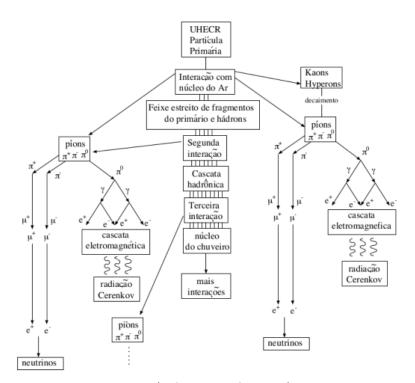

Os chuveiros atmosféricos intensos (EAS – Extensive Air Shower) são produzidos pelo contato do raio cósmico com a atmosfera. Esses chuveiros são compostos por milhões de partículas que se espalham por um raio de milhares de metros em alguns nanosegundos. O EAS tem mais de 10000 partículas e é produzido por uma partícula primária de energia maior que 10<sup>14</sup>eV (BANDEIRA, 2018). Na Figura 2 é possível ver um fluxograma com as componentes dos chuveiros atmosféricos.

Figura 2: Fluxograma esquemático representando toda a estrutura de um chuveiro atmosférico

Fonte: (BANDEIRA, 2018)

O chuveiro se subdivide em 3 componentes: eletromagnética, componente hadrônica e componente múonica. A cascata hadrônica é a parte que está mais próxima ao centro do chuveiro, esses processos de interação hadrônica são de curta duração e geram um caráter eletromagnético através da produção de pares e do decaimento de píons (BANDEIRA, 2018).

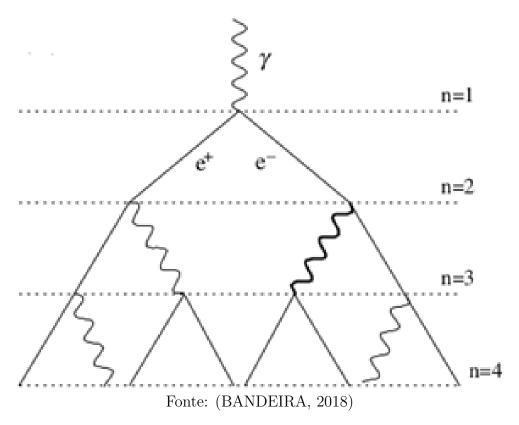

#### 1.4.2. Cascata Eletromagnética

Como a interação hadrônica na atmosfera se comporta como se o processo eletromagnético fosse mais importante podemos inclui-la também na cascata eletromagnética. Um fóton cruza uma distância antes de formar um par elétron-positron, com metade da energia inicial . Após isso percorre mais uma distância antes do elétron sofrer uma desaceleração e produzir um fóton com a metade da energia anterior. Assim os fótons, elétrons e pósitrons passarão por sucessivos desdobramentos até que a produção de pares eletron-ion seja muito baixa (BANDEIRA, 2018).

Cada elétron passa por sucessivos desdobramentos, sofrendo perdas de energia e produzindo fótons. A distância percorrida ( $\chi$ ) após n desdobramentos é  $\chi = n\lambda_r ln(2)$  (onde n é o número de partículas,  $\lambda_r$  é o comprimento de interação das partículas eletromagnéticas no meio e o termo ln(2) corresponde a distância em que um elétron perde metade de sua energia) e o número de partículas é 2n, cada desdobramento ocorre após uma distância d. O processo continua até que a energia média das partículas seja menor que uma energia crítica, onde predominam processos de ionização.(BANDEIRA, 2018). Na Figura 3 é possível observar um exemplo de formação da cascata eletromagnética.

Figura 3: Ilustração do modelo de Heitler, onde temos um elétron realizando sucessivos desdobramentos a cada distância d.

O chuveiro atinge sua máxima largura e máximo número de partículas quando a energia média da cascata é igual à energia crítica. O número total de partículas nesse

ponto é proporcional à energia incidente. O desenvolvimento da cascata é descrito matematicamente, com expressões que relacionam a profundidade do máximo do chuveiro com a energia incidente (BANDEIRA, 2018).

#### 1.4.3. Cascata Hadrônica

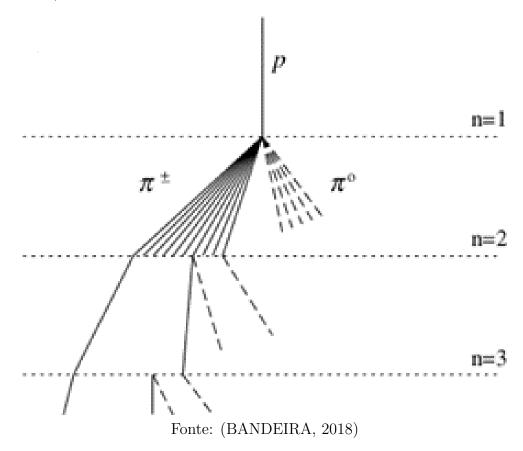

O modelo de Heitler pode ser estendido para incluir interações hadrônicas, resultando no modelo de Heitler-Matthews. Nesse modelo, a atmosfera é dividida em camadas, onde partículas hadrônicas interagem inelasticamente com núcleos atmosféricos, gerando píons secundários carregados e neutros. Na Figura 4 é possível observar um modelo esquemático da cascata hadrônica (BANDEIRA, 2018).

Os píons carregados propagam-se, interagindo e gerando mais píons em camadas subsequentes, até atingirem uma energia crítica. Os píons neutros, com vida curta, decaem rapidamente em fótons, dando origem a uma cascata eletromagnética. Esse processo continua até que os píons carregados atinjam uma energia crítica, abaixo da qual decaem em múons. Os múons produzidos também decaem posteriormente (BANDEIRA, 2018).

Figura 4: Ilustração do modelo de Heilter-Matthews, onde temos um raio cósmico realizando sua primeira interação à profundidade de  $\chi^0$  e produzindo píons carregados,  $\pi^{\pm}$ , e píons neutros,  $\pi^0$ .

O número de píons carregados e múons é relacionado à energia primária e à taxa

de interações. A profundidade do máximo do chuveiro é determinada pela cascata eletromagnética resultante do decaimento dos píons neutros gerados na primeira interação hadrônica. A taxa de elongação dos chuveiros iniciados por hádrons é determinada pelo comprimento de radiação, multiplicidade de partículas secundárias e pela interação próton-ar. Porém, alguns parâmetros precisam ser interpretados com cuidado devido às simplificações do modelo. A posição do máximo do chuveiro é afetada por flutuações na primeira interação e perda de energia subsequente (BANDEIRA, 2018).

## 1.5. Interação de raios cósmicos com semicondutores

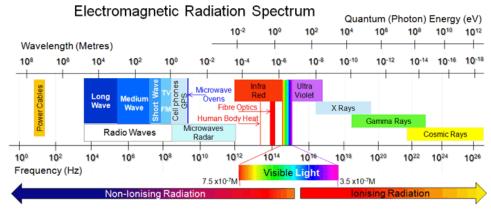

Figura 5: Ilustração do modelo de Heilter-Matthews, onde temos um raio cósmico realizando sua primeira interação à profundidade de  $\chi^0$  e produzindo píons carregados (denotados por  $\pi^{\pm}$ ) e píons neutros (denotados por  $\pi^0$ ).

Fonte: (ELECTROPEDIA, 2023)

Como já mencionado os raios cósmicos são partículas de alta energia, principalmente prótons e núcleos atômicos, que se originam no espaço exterior e viajam em altas velocidades através do universo. A faixa de energia dos raios cósmicos são bem altas como pode ser visto na Figura 5. Quando essas partículas carregadas interagem com diferentes materiais semicondutores das fámilias II, III, IV, V e VI da tabela periódica. Ocorrem diversas interações e processos que podem afetar o desempenho desses dispositivos uma vez que o gap de energia dos semicondutores é entre 1eV e 3,6eV. Algumas das principais formas pelas quais os raios cósmicos interagem com o silício são citadas abaixo:

❖ Ionização: As partículas carregadas dos raios cósmicos possuem energia suficiente para ionizar átomos do silício. Isso significa que eles podem arrancar elétrons dos átomos de silício, criando pares de elétrons e lacunas (buracos de elétrons) no material semicondutor. Esses elétrons e lacunas podem influenciar o comportamento elétrico dos dispositivos.

❖ Geração de Cargas: A ionização causada pelas partículas dos raios cósmicos resulta na geração de cargas elétricas dentro do material semicondutor. Isso pode afetar o funcionamento de dispositivos eletrônicos, causando correntes indesejadas e mudanças na operação normal.

- ❖ Alterações Estruturais: As partículas dos raios cósmicos também podem causar danos físicos aos átomos do silício, levando a alterações na estrutura cristalina do material. Essas alterações podem influenciar as propriedades elétricas dos semicondutores.

- ❖ Introdução de Defeitos: A alta energia das partículas dos raios cósmicos pode introduzir defeitos no cristal de silício, como vacâncias (locais onde átomos estão faltando) e intersticiais (átomos que se alojam em posições não regulares na estrutura cristalina). Esses defeitos podem afetar a mobilidade dos elétrons e lacunas no material.

- ❖ Efeito Cumulativo: A exposição contínua aos raios cósmicos pode causar danos acumulativos ao material semicondutor ao longo do tempo. Isso pode resultar em degradação gradual do desempenho dos dispositivos.

Em resumo, esses efeitos podem afetar a operação e a confiabilidade dos dispositivos eletrônicos que utilizam silício como material semicondutor. Portanto, é importante considerar os efeitos dos raios cósmicos ao projetar sistemas eletrônicos em ambientes onde a exposição a essas partículas de alta energia é uma preocupação.

### 2. Desenvolvimento

# 2.1. Primeira Geração de Pesquisas

Com o avanço da tecnologia século XX e a corrida espacial durante a Guerra Fria houveram diversos avanços nos uso de equipamentos elétricos e eletrônicos, seu uso em satélites e construção de foguetes que trouxeram junto diversos avanços em outras áreas como geração de energia, indústrias, máquinas hospitalares, computadores pessoais e robótica.

Com isso fez-se necessário estudar as fontes de erro que poderiam causar defeitos nesses equipamentos. No caso de satélites e foguetes era essencial minizar as falhas uma vez que após o lançamento o reparo seria complexo.

#### 2.1.1. Memória RAM

A memória RAM (Random Acess Memory) é uma memória de acesso aleatório. Conexão entre a memória e o processador ocorre de forma direta ou indireta por meio de um

barramento de memória. Esse barramento é composto por dois componentes essenciais: o barramento de endereço e o barramento de dados. Inicialmente, o processador transmite um valor, denominado endereço de memória, através do barramento de endereço. Esse endereço indica a posição na qual os dados desejados estão localizados na memória. Em seguida, o processador efetua a leitura ou escrita dos dados, que são colocados no barramento de dados. As memórias RAM possuem uma característica volátil, o que significa que o armazenamento das informações perdura somente enquanto houver fornecimento de energia ao computador (FERNANDEZ, 2015).

Essas memórias são construídas a partir de circuitos lógicos utilizando transistores, resistores e capacitores. E podem ser classificadas como memória estática ou dinâmica.

A memória RAM Estática é construída com chaves ON/OFF (Flip-flops) que armazenam os bits. Os dados mantêm-se sem necessidade de atualização, mesmo quando desligada. Sua fabricação é complexa e ocupa espaço considerável, tornando-a mais dispendiosa. A vantagem é sua alta velocidade, tornando-a ideal para memória cache (FERNANDEZ, 2015).

A Memória RAM Dinâmica utiliza capacitores para armazenar os bits, porém estes se descarregam com o tempo, demandando um processo de "refresh" para preservar os valores. Embora requeira um circuito dedicado para o "refresh", sua construção é mais simples, compacta e econômica, permitindo módulos de memória maiores. Contudo, é mais lenta que a RAM estática, sendo mais apropriada para a memória principal. O circuito de "refresh", geralmente integrado no chip, reescreve os dados para regenerar as informações, resultando em uma redução do desempenho do sistema (FERNANDEZ, 2015).

A historia do computador eletrônico passa por gerações. Sendo a primeira de 1943 até 1959, com computadores que funcionavam por poucas horas e funcionavam através de válvulas (que substiruiram relés eletromecânicos). A segunda geração foi de 1959 a 1965 com a substituição das válvulas por transistor que eram mais rápidos nos cálculos. A terceira geração foi de 1965 a 1970 com a susbtiruição dos transistores por circuitos integrados (CI) com diversos transistores e componentes eletrônicos acomplados em um único substrato. A quarta geração se iniciou em 1970 e segue até hoje, começando com a utilização de microprocessadores reunindo em um único ci todas as funções do computador (FERNANDEZ, 2015).

Suc Contract of the contract o

Figura 6: Réplica do primeiro transistor desenvolvido em 1947

Fonte: (RICHARDS, 2023)

Em 1959, um computador transistorizado continha 150.000 transistores ocupando 10 m². Tais transistores eram significativamente menores que as válvulas eletrônicas que substituíram, mas ainda eram entidades individuais que requeriam montagem individual. Contudo, durante os anos 80, a mesma quantidade de transistores podia ser produzida simultaneamente em um único circuito integrado. Para contextualizar, um processador moderno como o i7 passa de 1,7 bilhões de transistores, todos fabricados simultaneamente em uma pastilha de silício do tamanho de uma unha (FERNANDEZ, 2015).

#### 2.1.2. Erros suaves em memórias RAM

Os primeiros estudos voltados a erros causados pelos raios cósmicos eram quase totalmente em relação a erros nas memórias RAM que estavam presentes em dispositivos que coletavam dados já fora da atmosfera terrestre como satélites.

Em 1962 uma hipótese de que íons pesados de raios cósmicos causariam erros temporários e aleatórios de bits em memórias de satélites à medida que aumentassem a densidade de empacotamento foi apresentada em um artigo de J. T. Wallmark e S. M. Marcus. Porém apenas em 1975 evidências que confirmam essa previsão foram apresentadas em um artigo de D. Binder, E. C. Smith e A. B. Holman, em relação a um disparo anômalo de circuitos flip-flop bipolares em um satélite de comunicações (PICKEL; BLANDFORD, 1980).

Assim houve a definição do chamado "erros transitório" ou "erro suave" também conhecido como "soft error" como sendo erros aleatórios e não recorrentes em dispositivos de memória, afetando apenas um único bit. Esses erros não são permanentes, ou seja, nenhum defeito físico está associado ao bit defeituoso. Na verdade, um bit que apresenta um erro transitório é completamente recuperado no ciclo de escrita subsequente, sem

maior probabilidade de apresentar um erro do que qualquer outro bit no dispositivo (MAY; WOODS, 1978).

Quando o erro resultante é soft. Não há dano físico à célula; apenas seu conteúdo foi alterado, e novas informações escritas na célula serão mantidas no estado correto. Na prática, os erros suaves têm uma duração finita em um sistema. Eles são continuamente apagados por meio da reescrita que ocorre à medida que as informações são movidas para dentro e para fora do sistema. Os erros suaves não são apagados pela atualização periódica de corrente de vazamento em uma memória dinâmica. O estado da célula é detectado no chip; as informações não passam pelo circuito de correção de erros e qualquer estado errôneo é reescrito de volta na célula. Da mesma forma, quando uma célula de memória é acessada, a mesma passa pelo circuito de correção de erros, mas uma célula corrigida normalmente não é reescrita de volta na memória (NOORLAG; TERMAN; KONHEIM, 1980).

Um erro "duro" é aquele que pode ser considerado permanentemente não confiável e geralmente fica preso em um estado binário ou outro. Ao contrário de um erro "suave", não pode ser corrigido. Erros duros ocorrem devido a falhas nos componentes de memória, como um chip desenvolvendo uma abertura ou curto, e geralmente ocorrem devido ao envelhecimento dos componentes do sistema (NOORLAG; TERMAN; KONHEIM, 1980).

No caso em que não há uma correção, os erros suaves se acumulam com o tempo, como se fossem erros duros. Quanto mais curto for o intervalo de apagamento, menor a probabilidade de uma palavra adquirir mais de um erro suave em um determinado intervalo de tempo. No caso limite de apagamento efetivamente instantâneo dos erros suaves, a probabilidade de uma palavra adquirir dois erros suaves é praticamente zero. Taxas muito altas de geração de erros suaves podem ser tratadas tornando o intervalo de apagamento suficientemente curto, desde que não haja erros duros presentes (NOORLAG; TERMAN; KONHEIM, 1980).

Segundo Timothy C. May e Murray H. Woods (MAY; WOODS, 1978) a indústria de semicondutores em 1978 observava uma tendência contínua em direção a um aumento nos níveis de integração nos circuitos de memória. As memórias de acesso aleatório (RAMs) evoluíram desde as DRAMs de 1K com células de 3 transistores, lançadas em 1971, até as DRAMs de 4K com célula de 1 transistor, introduzidas em 1974, e, posteriormente, até as DRAMs de 16K com células "meio-transistor", primeiramente introduzidas em 1976. E em 1978, estavam sendo projetadas RAMs mais densas, com capacidade de 64K-bits (MAY; WOODS, 1978). Hoje temos RAMs com capacidade de até 128GB e assim como em 1978 podemos esperar que a tendência de maiores densidades de memória continue crescendo.

Na Figura 7 é possível observar a grande evolução e diminuição do tamanho de transistores desde seu lançamento em 1947. Sua evolução tornou possível o desenvolvimento de diversas tecnologias, entre elas as memórias RAM.

Treatment of the protection of

Figura 7: Linha do tempo de evolução do transistor

Fonte: (CORPORATION, 2022)

As memórias dinâmicas armazenam dados como presença ou ausência de carga minoritária de portadores nos capacitores de armazenamento. É necessário fazer uma atualização periódica para manter a carga armazenada. Para RAMs (Memórias de Acesso Aleatório) de canal-n e CCDs (Dispositivos de Carga Acoplada) de canal-n, as cargas são elétrons e os capacitores assumem a forma de poços de potencial no silício do tipo p, sob eletrodos de polissilício carregados positivamente. A quantidade de carga que poderia ser armazenada geralmente ficava na faixa de 300.000 a 3.000.000 de elétrons. No entanto, o número de elétrons que diferencia os poços "vazios" dos "cheios" é reduzido por efeitos como transferência incompleta de carga para as linhas de bit dos amplificadores de leitura, sensibilidade do amplificador de leitura e geração térmica. O número de elétrons que diferencia um "1" de um "0" é definido como "carga crítica", Qcrit (MAY; WOODS, 1978).

A falha de atualização desses poços vazios em memórias dinâmicas, para reter seus dados, seja quando expostos a luz suficiente ou a uma temperatura elevada, é devido ao preenchimento desses poços com elétrons gerados. Pares elétron-buraco são gerados pelas partículas alfa à medida que elas desaceleram e podem ser coletadas por camadas de depleção de modo que os elétrons gerados acabem em poços de armazenamento. Se a fração coletada multiplicada pelo número gerado exceder Qcrit, resultará em um "erro suave" (soft error). Uma única partícula alfa é capaz de causar um erro transitório em algumas RAMs sensíveis de 4K e 16K. Já as memórias de 64K-bits apresentaram taxas consideráveis de erros suaves (MAY; WOODS, 1978).

Em 1978 um estudo relativo à um mecanismo físico que gerava erros nas memórias para que fosse possível determinar o menor tamanho físico possível das memórias na época sem que a taxa de os erros gerados fossem grandes ou pudessem tornar os dados coletados e salvos na memória fossem errôneos foi realizado por Timothy C. May e Murray H. Woods.

Erros transitórios em sistemas de memória dinâmica foram previamente atribuídos a "ruído do sistema", "marginalidade de tensão", "amplificadores de leitura" ou "sensibilidade a padrões". No entanto, o fenômeno relatado é um mecanismo físico, não estatístico. Ao discutir as taxas de erros transitórios, os pesquisadores pressupôs que as fontes mencionadas acima foram eliminadas. A importância desse mecanismo é que ele não pode ser eliminado por procedimentos padrão de redução de ruído; somente um projeto adequado do próprio dispositivo de memória poderia eliminar esses erros transitórios (MAY; WOODS, 1978).

No experimento, os portadores (elétrons e buracos) gerados nas camadas de depleção que cercam regiões sob portas são separados por campos elétricos. Em tecnologias de canal-n, os elétrons são direcionados para poços de armazenamento e os buracos para o substrato. A "eficiência de coleta", que mede a fração de portadores coletados em relação ao número total gerado em uma região, é próxima de 100%, limitada apenas pela recombinação relativamente pequena que ocorre. Os elétrons e buracos gerados fora das regiões de depleção difundem-se pelo silício e, quando atingem a borda da camada de depleção, são direcionados para as regiões de armazenamento ou relaxados ohmicamente através do contato do substrato. O processo de coleta de corrente atinge o pico rapidamente após a geração no silício e é concluído em microssegundos (MAY; WOODS, 1978).

A taxa real de erros suaves de uma estrutura de teste específica ou dispositivo real depende de vários fatores: fluxo e energia da radiação ionizante, área-alvo, carga crítica, eficiência de coleta, geometria das células, entre outros. Esses fatores, por sua vez, são função do design do dispositivo, dos parâmetros tecnológicos e do tipo e composição da embalagem (MAY; WOODS, 1978).

Os primeiros dois resultados obtidos no estudo foram confirmados para certas matrizes dinâmicas através de varreduras raster de dispositivos individuais incorporando um padrão de dados com metade de "1"s e metade de "0"s. Quando essas matrizes foram expostas a fontes intensas de partículas alfa de Po-210, com energia máxima das partículas alfa de 5,31MeV, apenas metade da matriz com um padrão de dados de "1"s sólidos (poços vazios) apresentou erros suaves, os quais estavam distribuídos aleatoriamente. Nem todas as memórias dinâmicas apresentam apenas erros suaves de  $1\div0$ . Por exemplo, se o padrão de dados for invertido internamente, pode parecer externamente que ocorreu um erro suave de  $0\div1$ . Além disso, em alguns dispositivos, elétrons coletados por nós flutuantes em outras partes do circuito podem contribuir para erros suaves (MAY; WOODS, 1978).

Através do experimento em sistemas com memórias dinâmicas contendo até 64K-bits pode-se observar que erros suaves podem ser causados por partículas alfa. Além disso, fontes artificiais como polônio-210 e tório-230, bem como fontes naturais como minerais de urânio/tório, foram utilizadas para produzir erros suaves em estruturas de teste sensíveis a fim de obter um resultado semelhante ao produzido por partículas alfa naturalmente

#### (MAY; WOODS, 1978).

As partículas alfas interagem fortemente com a matéria devido à sua carga. Uma partícula alfa de 4MeV entrando no silício inicialmente tem uma velocidade de 0,05c, ou seja, 6000km/h e perde energia a uma taxa de dE/dx =  $150~{\rm KeV/\mu m}$ . O número de pares elétron-buraco produzidos por unidade de comprimento é determinado pela energia média necessária para produzir um par elétron-buraco no silício. Esse número foi medido para geração por partículas altamente energéticas e é de  $3,6eV/{\rm par}$  elétron-buraco (MAY; WOODS, 1978).

Outras propriedades das partículas alfa que são críticas para a modelagem de erros suaves são sua trajetória, dispersão, a absorção por fontes mais espessas e sua característica nuclear que dificulta sua modificação por temperatura e pressão (MAY; WOODS, 1978). O erro causado por partículas alfa pode ser observado a partir dos anos 1970 por conta de seu alcance ter dimensões comparável com a dimensão dos dispositivos desenvolvidos na época e podiam criar números de pares elétron-buraco comparáveis ao número necessário para causar perturbação de dados em algumas memórias dinâmicas. Essa é, é claro, a razão pela qual esse mecanismo só se tornou evidente em 1970 - gerações anteriores de dispositivos não eram afetadas pelas partículas alfa naturalmente presentes.

Figura 8: Chip Intel 1103: uma das primeiras memórias RAM comercializadas

Fonte: (WIKIPEDIA, 2023)

A possibilidade de que raios cósmicos ao nível do mar possam causar perturbações não era descartada, porém nessa época ainda era difícil realizar medições e experimentos com as partículas a essa altitude.

Outros fatores para a taxa de erro puderam ser observados. Um deles é o fluxo

de partículas alfa na superfície do chip que é facilmente calculado se as intensidades e localizações das fontes em relação ao chip forem conhecidas. Outro fator é a energia das partículas alfa que determina o número de pares elétron-buraco gerados no silício, o espectro de energia das partículas alfa é importante para determinar a fração de alfas capazes de causar erro. O terceiro fator é a eficiência de coleta representada pela fração do número total de elétrons gerados por alfas que são coletados pelos nós de armazenamento. Ela depende da área da célula, do ponto e profundidade de geração, do tempo de vida dos portadores minoritários na região p, das dimensões da região de depleção e da densidade de armadilhas. A área de uma célula de memória é importante no cálculo da "área alvo" total e é um fator na eficiência de coleta. Células grandes, para a mesma eficiência de coleta e Qcrit, resultarão em uma taxa de erros suaves maior do que células pequenas. No entanto, o tamanho de uma célula está geralmente diretamente relacionado ao tamanho da carga crítica, portanto, a evolução em direção a memórias mais densas e células menores tem levado, com algumas exceções recentes, a um Qcrit diminuído. Se o número de células por unidade de área for aumentado sem um aumento proporcional em erros/alfa (por exemplo, os erros/alfa atingiram a saturação em um), então, para um determinado fluxo alfa, a taxa de erro de bits na verdade diminui (MAY; WOODS, 1978).

Além desses fatores a geometria, composição e espessura das camadas de passivação de óxido atenuante podem afetar as taxas de erros suaves, especialmente para ângulos rasos de incidência de partículas alfa. O ângulo em que as partículas alfas atingem a superfície do dispositivo afeta não apenas a sua atenuação, mas também a sua profundidade de penetração, a eficiência de coleta dos portadores gerados e a área efetiva que o chip apresenta a um fluxo de partículas alfa entrantes (MAY; WOODS, 1978).

Em 1975 foi proposta pela primeira vez que raios cósmicos seriam capazes de gerar disparos anômalos em circuitos digitais presentes em espaçonaves. Com isso em 1978 Kolasinki et al realizaram experimentos como objetivo de observar latches e erros nos dispositivos de memória de computadores da época.

Um latch é um circuito eletrônico básico utilizado na área de microeletrônica e sistemas digitais para armazenar um único bit de informação. Ele funciona como um elemento de memória primitivo, permitindo que um valor de entrada seja retido e mantido em sua saída enquanto o circuito estiver ativo (PEREIRA, 2015).

Em termos simples, um latch tem duas entradas principais: uma entrada de dados (D) e uma entrada de controle (geralmente denotada como *Enable* ou E). Quando o sinal de controle está ativo, o valor presente na entrada de dados é transferido para a saída do latch, que pode ser interpretado como o valor armazenado. O valor permanece nesse estado até que o sinal de controle mude (PEREIRA, 2015).

Existem diferentes tipos de latches, sendo o "Latch D" (ou "Latch RS") e o "Latch JK" exemplos comuns. O Latch D possui uma entrada de dados (D) e uma entrada de controle (geralmente chamada de Clock). Ele armazena o valor de D na saída quando o

Clock é ativado. O Latch JK é uma versão mais avançada que possui duas entradas de controle (J e K), além de uma entrada de Clock. Ele permite não apenas a escrita de dados, mas também a capacidade de apagar ou inverter o valor armazenado, dependendo das entradas J e K. Os *flip-flops* são constituídos de latches e por isso levam o mesmos nomes, por exemplo, o flip-flop tipo D é constituído por dois latches D (PEREIRA, 2015).

Ao realizar o estudo, eles tinham três objetivos principais. Primeiro, demonstrar experimentalmente que de fato os raios cósmicos conseguiam induzir erros. Segundo testar aparelhos que já estavam incorporados em projetos que seriam lançados futuramente e encontrar meios de substituir peças que não fossem satisfatórias. E por fim, aprimorar e refinar os modelos já produzidos anteriormente. Os testes realizados nessa época eram realizados da seguinte maneira: utilizando um acelerador de partículas era gerado um feixe de íons, geralmente de ferro. Esse feixe era direcionado a atingir um chip de memória RAM que era previamente preenchida com várias sequências de 0 e 1 e quando detectado o erro de bits, durante a análise do endereço de memória, ele era registrado. Porém no estudo realizado em 1979 ainda era difícil quantificar com precisão os erros devido a falta de controle das propriedades do feixe utilizado (KOLASINSKI et al., 1979).

Os testes iniciais de Kolasinki foram feitos com feixes de íons de argônio. E após o ínicio do estudo foram alterados para ferro, pois os pesquisadores descobriram que o feixe de íons de ferro produzia erros de bits quando uma quantidade adequada de blindagem era colocada a montante do dispositivo de teste. Assim eles conseguiram demonstrar que após o contato com raios cósmicos erros e latch up eram gerados nas memórias estáticas de estado sólido. E que alguns modelos eram imunes a perturbação e podiam prever o desempenho do dispositivo de acordo com o modelo utilizado (KOLASINSKI et al., 1979).

Em 1980, um estudo demonstrou que à medida que as geometrias dos dispositivos diminuem para as tecnologias VLSI (Very Large Scale of Integrations) e menos carga é usada para representar um bit de dados, o problema de erro de bit induzido por um único íon se torna ainda mais grave(PICKEL; BLANDFORD, 1980). A tecnologia de VLSI em microeletrônica éutilizada para integrar uma grande quantidade de dispositivos eletrônicos numa única pastilha de silício.

Além dos raios cósmicos, existem outras fontes de radiação que podem causar tais erros: partículas de explosões solares que esporadicamente dominam o ambiente de radiação no espaço interplanetário, e partículas aprisionadas nas magnetosferas de planetas como a Terra. Além disso, colisões nucleares de partículas de alta energia geram ainda mais partículas que podem causar erros. A taxa na qual ocorrem erros suaves depende da frequência com que o circuito é atingido por uma partícula de raios cósmicos capaz de produzir a ionização necessária. Portanto, é necessário conhecer os espectros de energia e a composição elementar das partículas no espaço próximo à Terra (ADAMS; SILBER-BERG; TSAO, 1982).

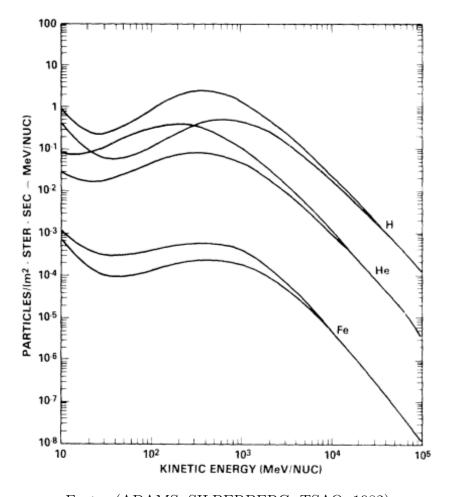

Na Figura 9 é possível observar o espectro de partículas de Ferro, Hélio e Hidrogênio

presentes e sua energia cinética em mega elétron-volts por núcleo.

A inclusão de estudos com núcleos de hidrogênio e hélio é particularmente importante para o projeto da próxima geração de computadores. Havia sido sugerido em trabalhos anteriores que aumentar a sensibilidade dos componentes de computador não aumentaria a frequência de perturbações. A partir deste trabalho (ADAMS; SILBERBERG; TSAO, 1982), pode-se ver que isso não é verdade e que a frequência de perturbações suaves aumentaria em ordens de magnitude quando prótons relativísticos pudessem gerá-las, assumindo que o volume sensível por bit permaneça constante. Também foi sugerido que, à medida que os dispositivos se tornam menores, sua densidade eletrônica operacional permanece constante. Isso leva a uma lei de escala na qual cada dimensão do volume sensível é reduzida por um fator a, o volume encolhe por  $a^3$  e o número de elétrons de condução necessários para produzir uma perturbação também encolhe por  $a^3$ . Isso significa que o mínimo LET (Linear Energy Transfer - Transferência Linear de Energia) típico necessário para produzir uma perturbação diminui por a.

Fonte: (ADAMS; SILBERBERG; TSAO, 1982)

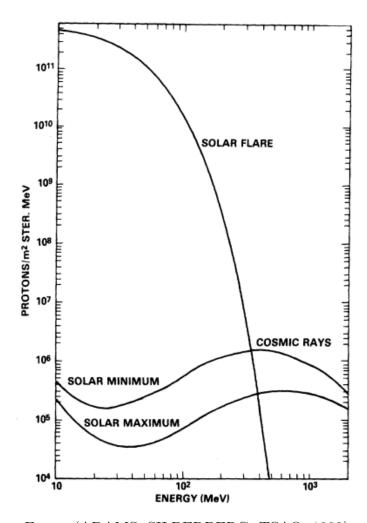

Cada um desses espectros possui dois ramos em baixas energias. O ramo superior corresponde a períodos de atividade solar mínima, enquanto o ramo inferior corresponde a condições de máxima atividade solar. A amplitude espectral varia entre esses extremos com um período de onze anos. Os ramos inferiores se aplicam durante 1981, enquanto os ramos superiores se aplicarão próximo a 1987. Além dos raios cósmicos, que estão sempre presentes no meio interplanetário, o ambiente de partículas ocasionalmente é enriquecido por grandes explosões solares. A Figura 10 mostra o espectro de prótons proveniente de uma série de explosões solares muito grandes que ocorreram em agosto de 1972. Também são mostrados, para comparação, os espectros de prótons de raios cósmicos que teriam se acumulado durante o período dessas explosões caso elas tivessem ocorrido durante o máximo e o mínimo solar, respectivamente (ADAMS; SILBERBERG; TSAO, 1982).

Figura 10: O espectro de energia diferencial de hidrogênio acumulado para as explosões solares de 4 de agosto 1972 a 10 de agosto de 1972. Isso é comparado com o espectros de hidrogênio de raios cósmicos galácticos acumulados por uma semana no máximo solar e mínimo respectivamente.

Fonte: (ADAMS; SILBERBERG; TSAO, 1982)

#### 2.1.3. Correção de erros suaves na primeira geração

Para corrigir e evitar os erros causados algumas técnicas foram desenvolvidas. A técnica mais simples e frequentemente utilizada para lidar com erros suaves em circuitos lógicos consiste em duplicar os circuitos afetados Uma máquina básica. A duplicação funciona bem enquanto os módulos falham de forma independente. Uma técnica alternativa e geral chamada Filtragem de Erros Suaves (SEF, sigla em inglês). No SEF, a redundância assume a forma de filtros incluídos entre a saída de uma rede lógica combinacional e o registrador de saída. Os filtros removem os transitórios curtos que causam erros suaves. Essa abordagem permite uma sobrecarga de hardware baixa, uma vez que a função lógica não é replicada. Além disso, se os transitórios forem muito mais curtos do que o período de clock, a sobrecarga de tempo também é pequena (SAVARIA et al., 1986).

Um exemplo de técnica de nível físico é revestir o chip com uma camada de material contendo pouquíssimas impurezas radioativas. Essa camada tem uma espessura suficiente para absorver as partículas alfa emitidas pelos materiais de embalagem. Essa abordagem é relativamente barata, mas tem uma eficiência limitada, uma vez que os materiais que compõem o próprio circuito contêm traços significativos de elementos radioativos (SAVA-RIA et al., 1986).

Um segundo exemplo de solução de nível físico é aumentar a capacitância dos nós internos para um nível em que a carga injetada por partículas alfa seja insuficiente para causar um erro. Essa abordagem requer aumento da área e maior consumo de energia, que deve ser dissipada. Esses dois exemplos ilustram uma tendência geral; as abordagens físicas aumentam os custos e têm valor decrescente à medida que a densidade dos circuitos aumenta. [9] As abordagens de nível de sistema consistem em redundância de hardware ou de tempo. Por exemplo, a Redundância Modular Triplicada (TMR) usa três módulos em paralelo (SAVARIA et al., 1986).

O Soft-Error Filtering (SEF) permite a implementação de máquinas tolerantes a erros suaves, sem as limitações das técnicas de nível físico e com menos sobrecarga do que as técnicas convencionais de nível de sistema. Esse modelo estabelece a necessidade de um latch de filtragem, que foi otimizado para filtrar transientes em seus dados de entrada (SAVARIA et al., 1986).

A abordagem SEF para o projeto de sistemas digitais tolerantes a erros suaves baseia-se na suposição de que é possível construir um registro que possa filtrar transitórios em sua entrada. Esses transitórios podem ser significativamente mais longos do que o tempo básico de comutação da tecnologia utilizada. Além disso, o espaço e o tempo associados aos registros devem ser aceitavelmente baixos. Além disso, é implícito na técnica SEF que os registros devem ser intrinsecamente tolerantes a fontes de erros suaves, como impactos diretos de partículas alfa (SAVARIA et al., 1986).

#### 2.1.4. O modelo CREME

Em 1981 foi criado o CREME (Cosmic Ray Effects on Micro-Electronics). O modelo CREME é um conjunto de códigos de computador desenvolvido para prever os efeitos das partículas carregadas de alta energia, especialmente os raios cósmicos galácticos (GCR), nos dispositivos de microeletrônica usados em satélites e espaçonaves. Ele foi criado para entender melhor os impactos das partículas carregadas nas memórias e nos circuitos eletrônicos dos dispositivos, que podem causar perturbações conhecidas como "single-event upsets" (SEUs) (UNIVERSITY, 2023).

Em 1996 houve uma atualização dos códigos que visava algumas alterações como a criação modelos numéricos do ambiente de radiação ionizante em órbitas próximas à Terra, avaliar os efeitos resultantes da radiação em sistemas eletrônicos em espaçonaves e aeronaves de alta altitude, estimar o ambiente de radiação de alta LET dentro de espaçonaves tripuladas (UNIVERSITY, 2023).

Em 2011 foi liberada uma nova atualização do código CRÈME que foi atualizado pela última vez em 1996, durante este período, descobriu-se que a modulação dos raios cósmicos galácticos tinha não apenas um ciclo de onze anos, mas também um ciclo de vinte e dois anos. Além disso, descobriu-se também que os eventos ricos em hélio pequenos eram enriquecidos em íons pesados. Isso explicou grande parte da dispersão na composição elemental incluída no CREME86. As partículas solares energéticas (SEPs) foram descobertas sendo aceleradas em ejeções de massa coronal (CMEs). Com esta versão, também adicionamos uma nova ferramenta computacional de Monte Carlo chamada CREME-MC. O CRÉME-MC é, na verdade, implementado pelo MRED, um aplicativo Geant4 com extensões em Fortran desenvolvidas em Vanderbilt. O MRED tem sido amplamente utilizado para investigações dos efeitos da radiação em microeletrônicos. Um crescente conjunto de evidências tem demonstrado que, em muitos casos, a simulação física é o único método apropriado para estimar as taxas de erro. As técnicas de resistência à radiação, muitas vezes, introduzem intencionalmente nós de circuito redundantes em um projeto e invalidam a suposição de volume único sensível dos modelos antigos. Reações nucleares induzidas por íons têm sido mostradas causando falhas pontuais induzidas por evento único, e reações nucleares a partir de prótons (e íons por extrapolação) têm mostrado exibir uma resposta angular para alguns circuitos (ADAMS et al., 2012).

### 2.2. Segunda Geração de Pesquisas

A partir dos anos 1990 começaram a ser realizados diversos estudos sobre erros causados por raios cósmicos não só em dispositivos de memória, mas também em dispositivos eletrônicos de potência. Diversas empresas de semicondutores começaram a financiar essas pesquisas como IBM, ABB, Intel, Fujitsu, além de empresas aeroespaciais e organizações governamentais.

#### 2.2.1. Falhas em dispositivos de potência

Dispositivos de alta potência baseados em semicondutores são meticulosamente concebidos para assegurar uma vida útil superior a 25 anos em operação contínua. Essa garantia é respaldada por uma bateria de testes abrangentes e pela manutenção de padrões rigorosos de excelência. Recentemente, durante análises de estabilidade a longo prazo, que incluíram a aplicação de tensões elevadas em corrente contínua, surgiu uma forma de falha previamente desconhecida e inesperada. Essa anomalia aparenta ter uma natureza estatística, acrescentando complexidade ao cenário (KABZA et al., 1994).

A peculiaridade desse padrão de falha reside na manifestação súbita de um curtocircuito imprevisto. Os dispositivos afetados exibem a formação de um canal derretido, cujo diâmetro não ultrapassa o de uma agulha, estendendo-se do cátodo ao ânodo. Essa distorção é capaz de ocorrer em qualquer ponto dentro do volume do dispositivo. A identificação do mecanismo subjacente e das causas subjacentes a tais falhas tem sido um processo multifacetado, envolvendo a condução de numerosos experimentos em conjunto com simulações computacionais detalhadas (KABZA et al., 1994).

Tal falha causada por raios cósmicos afeta diodos, tiristores e GTOs (Gate Turn-Off Thyristors). E consiste em uma quebra localizada no interior do dispositivo e não está relacionada a instabilidades do terminal de junção. O início da quebra ocorre sem um precursor e em poucos nanossegundos. A taxa de falha é constante ao longo do tempo, fortemente dependente da tensão aplicada e praticamente independente da temperatura. O efeito é reduzido por blindagem e, portanto, acredita-se geralmente que a falha seja induzida por raios cósmicos (ZELLER, 1994).

No estudo realizado por Zeller em parceria com a ABB (Empresa fabricantes de produtos elétricos e eletrônicos) foi observado que um GTO de 3000A é penetrado por cerca de um p méson por segundo ao nível do mar. Nas tensões nominais de bloqueio, as taxas de falha observadas são inferiores a  $1 \cdot 10^{-6} s^{-1}$ , o que mostra que um modelo baseado em propriedades médias de mésons não explicaria o fenômeno. Um méson com incidência normal depositará no máximo alguns MeV de energia no dispositivo, criando não mais que  $1 \cdot 10^6$  pares elétron-lacuna. Isso está muito abaixo do limiar de dano térmico e, uma vez que o campo elétrico está abaixo do limiar para ionização de impacto, mecanismos de aprimoramento de campo devem ser invocados para levar à multiplicação de portadores e, eventualmente, à destruição. Foi demonstrado por simulação numérica que os campos autogerados pelo plasma induzido pela partícula não atingem valores perigosos. No entanto, se o plasma estiver concentrado em um defeito de linha, então campos autogerados acima do limiar de multiplicação são facilmente produzidos. Através desse conhecimento é possível deduzir regras de design para dispositivos confiáveis (ZELLER, 1994).

Em 1998 (FINDEISEN et al., 1998) realizou experimentos com IGBTs e diodos de módulos usando um feixe de nêutrons no LANSCE (Los Alamos Neutron Science Center)

em Los Alamos, NM, EUA. O fluxo de nêutrons desse feixe é oito ordens de magnitude mais intenso do que o componente de nêutrons dos raios cósmicos ao nível do mar. Além disso, as distribuições de energia de ambos os nêutrons são semelhantes até 800 MeV. Durante o experimento, o feixe de nêutrons atravessou 12 ou 24 camadas de chips de IGBT ou diodos de módulo polarizados. Os valores do fluxo de nêutrons, da corrente de fuga de todos os subconjuntos (cada um consistindo de quatro chips polarizados em paralelo) e do monitor de polarização foram registrados para cada execução a uma taxa de 0,5 Hz. Cerca de 1000 chips de IGBT e diodos de módulo de duas classes diferentes de alta tensão (2,5 e 3,3 kV) foram testados em vários níveis de polarização. Nem o fluxo de nêutrons nem a distribuição de energia foram alterados. A redução do fluxo de nêutrons após 24 camadas, devido a interações nucleares entre os nêutrons e os subconjuntos, foi inferior a 25%.

Uma falha foi definida quando eventos irreversíveis ocorreram. Um evento era um aumento súbito e irreversível na corrente de fuga em mais de um fator de 10 (falha paramétrica), o outro evento era a perda da capacidade de bloqueio devido à formação de um filamento de silício derretido (falha catastrófica). Quase todas as falhas observadas foram catastróficas. O dano físico dos chips que falharam catastroficamente foi analisado. Quando necessário, o local do defeito foi localizado por meio de detecção de pontos quentes de cristais líquidos. O padrão típico de falha foi silício derretido na área do chip e um canal derretido que se estende por todo o dispositivo. Os diodos têm uma junção quase abrupta, suas taxas de falha seguem uma curva paralela à curva do GTO e o deslocamento em comparação com a curva do GTO é consistente com a diferença esperada entre uma junção abrupta e uma junção profunda. Os resultados do IGBT são mais complexos. O IGBT também tem uma junção quase abrupta, mas além disso, a distribuição de campo elétrico não é unidimensional como em dispositivos de potência bipolares como diodos, GTOs e tiristores (FINDEISEN et al., 1998).

#### 2.2.2. Dispositivos CMOS e MOSFET

A partir do uso em larga escala dos chips produzidos com CMOS nos anos 1990 surgiram mais pesquisas sobre as falhas causadas por radiação cósmica nesses dispositivos.

Segundo (HAZUCHA; SVENSSON, 2000) a dimensão do transistor CMOS é um fator importante para melhorar o desempenho das tecnologias que utilizam CMOS. E no estudo foi possível analisar a taxa de erro em circuitos fabricados em um processo CMOS comum e operando no ambiente natural do nível do solo até altitudes de voo de avião. No nível do mar, existem três principais contribuidores para a SER (Soft Error Rate, em português taxa de erros suaves), sendo o primeiro as partículas alfas emitidas por impurezas radioativas em decomposição em materiais de embalagem e interconexão, o segundo componente são nêutrons atmosféricos com energias abaixo de 1MeV, que interagem com o isótopo B presente em vidros horofosfossilicatos e regiões de tipo p e o

terceiro componente são nêutrons atmosféricos com energias 1MeV.

O estudo concluiu que a diminuição da escala será limitada pelo excesso de geração de calor ou pela SER causada por raios cósmicos. De fato, o excesso de geração de calor tornou-se um problema grave, especialmente em microprocessadores de alto desempenho, e tem sido uma das razões para a redução da tensão de alimentação. Infelizmente, uma tensão de alimentação mais baixa resulta em menor carga de comutação, o que aumenta a SER. Se apenas as dimensões fossem escaladas, mas não a tensão, a diminuição da carga seria linear, em vez de quadrática (HAZUCHA; SVENSSON, 2000).

Uma pesquisa interessante foi realizada utilizando amostragem temporal em latches para avaliar os efeitos de radiações ionizantes em dispositivos CMOS utilizando tecnologias SOI (silicon-on-insulator) e SOS (silicon-on-sapphire). Nessas tecnologias a separação e coleta de elétrons e lacunas ocorrem nas proximidades das junções dreno-bulk polarizadas reversamente dos transistores. O dispositivo bipolar parasita formado pelas regiões dreno-bulk-fonte de um transistor CMOS pode agravar o problema de injeção de carga, dependendo do ganho do parasita. Além disso, a redução da capacitância dos nós do circuito SOI e SOS amplifica a perturbação de tensão causada por uma quantidade dada de carga coletada. Essa tecnologia é menos suscetível a erros eu tecnologias em volume. Porém não são utilizadas em aplicações espaciais por serem muitos suscetíveis a erro fora da atmosfera terrestre. Para aplicações terrestres, as faixas relevantes de partículas carregadas são muito menores e esses dispositivos podem ser tornados muito imunes a perturbações se a separação dos nós críticos for mantida maior do que vários mícrons (MAVIS; EATON, 2002).

Nesse caso os latches projetados dão imunidade ao sistema para eventos de erro único e erros suaves. Isso por conta de serem redundantes física e temporalmente a perturbações estáticas que podem ocorrer nos próprios latches, transientes que podem ocorrer na lógica combinacional que antecede o latch e transiente que pode ocorrer no sinal de clock e controle do circuito (MAVIS; EATON, 2002).

Existem 4 tipos de perturbações que são evitadas pelo sistema de latch redundante utilizado (MAVIS; EATON, 2002).

- 1. O SEU (Single Event Upset ou evento de falha única) estático do latch ocorre quando um evento ionizante altera o estado de dados de um latch cujo clock está baixo e está em um estado de bloqueio (modo de retenção). A perturbação pode afetar qualquer um dos latches projetados e nos caminhos de liberação apenas um dos três nós estará com um sinal incorreto, assim como os outros dois sinais estão corretos o nó de saída irá apontar o valor correto.

- 2. O evento de erro de entrada ocorre quando a partícula carregada antige algum nó da lógica combinacional antes do latch de amostragem temporal e essa transição segue até a entrada com um sinal normal. Assim como no item 1, apenas um dos

caminhos apresentará erro e o nó de saída estará correto.

3. As partículas carregadas podem afetar a geração dos sinais de clock que podem fazer com que o latch seja alterado em momentos indesejados. Neste caso a alteração pode ocorrer em dois momentos. Existe uma gravação de dados do intervalo e se a alteração de borda do clock ocorrer antes do previsto na gravação a borda será considerada como da gravação.

4. Erro no clock de liberação pode causar uma falha no transiente. Caso o transiente seja apenas em um dos latches de amostragem então teremos o caso semelhante ao item 1 onde apenas um dos três nós terá sido alterado e a saída permanecerá correta. Caso o transiente seja comum para um grupo ou todos os latches o que ocorre é a liberação prematura dos resultados.

Neste caso é interessante observar em cada um dos quatro mecanismos de perturbação descritos acima é que qualquer dado errôneo armazenado em qualquer um dos latches de amostragem é descartado dentro de um único ciclo computacional (MAVIS; EATON, 2002).

Segundo (MAVIS; EATON, 2002) a principal contribuição deste trabalho foi mostrar como podemos usar a redundância temporal para substituir a redundância espacial a fim de alcançar imunidade total a erros induzidos por partículas alfa, nêutrons e raios cósmicos. Com a amostragem temporal, usamos efetivamente a mesma lógica combinacional em três momentos diferentes para produzir o equivalente à triplicação da redundância espacial.

Em um artigo publicado em 2005 foi realizada uma caracterização dos erros causado nos transistores MOSFET. Os erros são causados por rajadas concentradas de carga que atingem locais aleatórios do substrato do semicondutor e são coletadas pelos diodos de dreno do transistor MOS. Um fóton de luz visível é capaz de gerar um par eletrón-buraco no silício, as partículas alfas carregam uma energia bem maior que o fóton podendo gerar a alteração do estado lógico de um nó de circuito (KARNIK; HAZUCHA; PATEL, 2004).

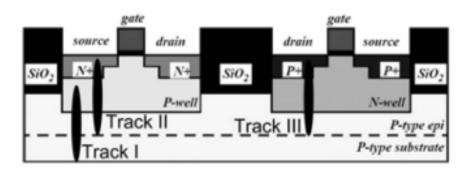

Figura 11: Exemplo de três trajetórias de partículas

Fonte: (KARNIK; HAZUCHA; PATEL, 2004)

A Figura 11 mostra um diagrama simplificado de MOSFETs do tipo N e P. Três trajetórias idênticas de partículas são mostradas em locais abaixo do dreno N+ (N+ drain), cruzando o dreno N+ e cruzando o dreno P+ e a junção P-N (N-well). Ao observar as curvas transientes de corrente presentes é possível observar que a carga coletada é siginificativamente menor que a carga gerada, a relação entre essas cargas é chamada de eficiência de coleta. A amplitude da trajetória II é maior que a trajetória I, isso ocorre pois I está localizada mais próxima ao dreno e tem uma sobreposição maior no volume coletado. Essa carga é dividida entre as duas junções PN, resultando em uma carga menor sendo coletada em um dreno P+ do que em um dreno N+. Há uma taxa de falhas muito menor nos drenos P+ em comparação com os drenos N+ (KARNIK; HAZUCHA; PATEL, 2004).

A dependência temporal e a quantidade total de carga coletada dependem da tensão aplicada ao diodo. A carga coletada e dependência temporal dependem da tensão aplicada no diodo. Assim se a tensão for maior a largura da região de depleção, profundidade de coleta e o volume aumentam, resultando em uma maior carga coletada. O aumento do campo elétrico na região de depleção faz com que o transiente de coleta seja mais rápido também (KARNIK; HAZUCHA; PATEL, 2004).

Um SEU (ou evento de falha única) é um evento transitório que dura cerca de 100ps. Durante esse tempo se a perturbação de carga no nó do circuito for menor que a margem de ruído o circuito opera normalmente. Caso contrário, se a tensão perturbada for maior então o circuito pode interpretar como um estado lógico diferente causando um funcionamento incorreto (KARNIK; HAZUCHA; PATEL, 2004).

Há diferença na resposta de circuitos dinâmicos e estáticos, com e sem feedback regenerativo. Um nó dinâmico é afetado pela carga total coletada e a mudança de tensão é inversamente proporcional à capacitância do nó. Um nó estático que tem um erro temporário eventualmente retornará ao seu estado original, a menos que haja feedback regenerativo que adicione ao erro e reverta o estado lógico do nó. Em um circuito ativamente sincronizado, um SEU em qualquer nó tem uma probabilidade finita de causar uma falha temporária que pode se propagar para uma entrada de uma célula sequencial, ser capturado como um valor incorreto e afetar o funcionamento da máquina (KARNIK; HAZUCHA; PATEL, 2004).

Em (SAGGESE et al., 2005) realizaram estudos com dois microprocessadores: o DLX para representar microprocessadores de sistemas embarcados e o Alpha para representar um microprocessador de alto desempenho. Para cada um foi usada uma tecnologia de design diferente, FPGA para o DLX e ASIC para o Alpha. Assim puderam quantificar o impacto dos erros transitórios em microprocessadores, os resultados obtidos foram:

♦ Máscara de falhas em nível de processador: uma porcentagem significativa de falhas injetadas (mais de 95% para DLX e 85% para Alpha) é mascarada na lógica ou nível arquitetural do processador; ou seja, as falhas não se manifestam nos pinos do

processador.

❖ Sensibilidade variável das falhas entre os blocos funcionais do processador: no processador DLX, os blocos de especulação são cinco vezes mais sensíveis a falhas (mais propensos a propagar falhas nos pinos do processador) do que os blocos de execução do processador. No processador Alpha, os flip-flops que armazenam informações sobre estados de fila e a validade de dados no processamento de dados são oito vezes mais sensíveis a falhas do que os flip-flops que representam campos de endereço para operações de memória.

- ❖ Erros lógicos combinacionais e sequenciais: cerca de 4% das falhas na lógica combinacional (para pulsos de tensão transitórios de um ciclo) e cerca de 10% das falhas na lógica sequencial se manifestam como erros nos pinos do processador.