## Universidade Federal de São Carlos PPG/CC - Programa de Pós-Graduação em Ciência da Computação Mestrado em Ciência da Computação

## RTEV - Ambiente de Desenvolvimento de Aplicações Reconfiguráveis com o Kernel de Tempo Real Virtuoso

Mairum Ceoldo Andrade

Orientador:

Prof. Dr. José Hiroki Saito

Co-orientador:

Prof. Dr. Célio Estevan Morón

SÃO CARLOS Julho, 2006

## Ficha catalográfica elaborada pelo DePT da Biblioteca Comunitária da UFSCar

A553ra

Andrade, Mairum Ceoldo.

RTEV - ambiente de desenvolvimento de aplicações reconfiguráveis com o kernel de tempo real Virtuoso / Mairum Ceoldo Andrade. -- São Carlos : UFSCar, 2009.

109 f.

Dissertação (Mestrado) -- Universidade Federal de São Carlos, 2006.

1. Computação reconfigurável. 2. FPGA - Field Programable Gate Array. 3. Virtuoso (Sistema operacional de computador). 4. Tempo real. I. Título.

CDD: 004.22 (20<sup>a</sup>)

## Universidade Federal de São Carlos

Centro de Ciências Exatas e de Tecnologia Programa de Pós-Graduação em Ciência da Computação

## "RTEV – Ambiente de Desenvolvimento de Aplicações Reconfiguráveis com o Kernel de Tempo Real Virtuoso"

#### MAIRUM CEOLDO ANDRADE

Dissertação de Mestrado apresentada ao Programa de Pós-Graduação em Ciência da Computação da Universidade Federal de São Carlos, como parte dos requisitos para a obtenção do título de Mestre em Ciência da Computação.

Membros da Banca:

Prof. Dr. José Hiroki Saito (Orientador – DC/UFSCar)

Prof. Dr. Célio Estevan Moron (Co-Orientador - DC/UFSCar)

Prof. Dr. Hélio Crestana Guardia

(DC/UFSCar)

Prof. Dr. Fábio Gonçalves Jota

(Depto. de Engenharia Eletrônica/UFMG)

São Carlos Agosto/2006

## Agradecimentos

Ao Prof. Dr. José Hiroki Saito, pela confiança e amizade, pelos ensinamentos, pela oportunidade de enveredar nos estudos de componentes reconfiguráveis, e extrema competência na orientação deste trabalho.

Ao Prof. Dr. Célio Estevan Morón, pelo apoio, auxilio no desenvolvimento e competência na coorientação deste trabalho.

Ao Prof. Dr. Hélio Crestana Guardia, pelo apoio, auxilio e considerações na banca de qualificação, que muito contribuiram no desenvolvimento deste trabalho.

A todos amigos do GAPIS e PPG-CC, pela amizade, apoio, convivío, troca de conhecimento, e momentos de descontração.

A minha família pelo amor, apoio, compreensão e incentivo que foram essenciais para conquista deste objetivo, e de todos os outros ao longo de toda a vida.

A todos, que de alguma forma, contribuiram para este objetivo fosse alcançado, direta ou indiretamente.

## Sumário

## Lista de Figuras

#### Lista de Tabelas

#### Resumo

#### Abstract

| 1 | Intro | odução   |                                                        | 14 |

|---|-------|----------|--------------------------------------------------------|----|

|   | 1.1   | Motiva   | ção e Relevância                                       | 14 |

|   | 1.2   | Objetiv  | ros e Definição do Problema                            | 16 |

|   | 1.3   | Estrutu  | ra do Texto da Dissertação                             | 16 |

| 2 | Revi  | isão Sob | re Arquiteturas Reconfiguráveis                        | 18 |

|   | 2.1   | Hardwa   | are X Software                                         | 18 |

|   | 2.2   | Vantage  | ens da Reconfiguração                                  | 20 |

|   |       | 2.2.1    | Tolerância a Falhas                                    | 20 |

|   |       | 2.2.2    | Prototipagem Rápida                                    | 20 |

|   |       | 2.2.3    | Tempo de Programação                                   | 21 |

|   |       | 2.2.4    | Área                                                   | 21 |

|   |       | 2.2.5    | Custo Financeiro                                       | 23 |

|   |       | 2.2.6    | Reconfiguração Parcial/Dinâmica                        | 24 |

|   | 2.3   | FPGA     |                                                        | 24 |

|   | 2.4   | Caracte  | erísticas e definições de arquiteturas reconfiguráveis | 25 |

|   |       | 2.4.1   | Acoplamento                                                     | 5 |

|---|-------|---------|-----------------------------------------------------------------|---|

|   |       | 2.4.2   | Granulosidade                                                   | 7 |

|   |       | 2.4.3   | Capacidade de Reconfiguração                                    | 3 |

|   | 2.5   | Consid  | erações Finais                                                  | 3 |

| 3 | Abo   | rdagens | para o Desenvolvimento de Aplicações Usando Arquiteturas Recon- |   |

|   | figui | ráveis  | 30                                                              | ) |

|   | 3.1   | Uma v   | são geral                                                       | ) |

|   | 3.2   | Projeto | s de Propósito Geral                                            | 3 |

|   |       | 3.2.1   | Abordagem de Anotações e Abordagem Dirigida por Restrições 34   | 1 |

|   |       |         | 3.2.1.1 SPC                                                     | 1 |

|   |       |         | 3.2.1.2 Streams-C                                               | 1 |

|   |       |         | 3.2.1.3 Sea Cucumber                                            | 5 |

|   |       |         | 3.2.1.4 SPARK                                                   | 5 |

|   |       |         | 3.2.1.5 Catapult-C                                              | 5 |

|   |       | 3.2.2   | Compilação Direta do Código Fonte                               | 5 |

|   |       |         | 3.2.2.1 ASC                                                     | 5 |

|   |       |         | 3.2.2.2 Handel-C                                                | 7 |

|   |       |         | 3.2.2.3 Haydn-C                                                 | 7 |

|   |       |         | 3.2.2.4 Bach-C                                                  | 3 |

|   | 3.3   | Projeto | s de Propósito Específicos                                      | 3 |

|   |       | 3.3.1   | Processamento Digital de Sinais                                 | 3 |

|   |       | 3.3.2   | Otimização da largura de dados                                  | ) |

|   |       | 3.3.3   | Outros métodos de desenvolvimento                               | ) |

|   |       |         | 3.3.3.1 CHAMPION                                                | ) |

|   |       |         | 3.3.3.2 IGOL Framework                                          | L |

|   |       |         | 2 2 2 2 SAC                                                     | 1 |

|   |       |        | 3.3.3.4 Framework para Firewall                                   | 41 |

|---|-------|--------|-------------------------------------------------------------------|----|

|   | 3.4   | Outros | Métodos                                                           | 42 |

|   |       | 3.4.1  | Customização em tempo de execução                                 | 12 |

|   |       | 3.4.2  | Processadores Soft e Hard                                         | 12 |

|   |       | 3.4.3  | Hardware/software Codesign                                        | 43 |

|   |       |        | 3.4.3.1 Garp                                                      | 43 |

|   |       |        | 3.4.3.2 NAPA C                                                    | 43 |

|   | 3.5   | Consid | derações Finais                                                   | 14 |

| 4 | Sista | mac (H | Iardware e Software) utilizados para o Desenvolvimento Proposto 4 | 45 |

| • |       |        |                                                                   |    |

|   | 4.1   | TEV .  |                                                                   | 46 |

|   |       | 4.1.1  | GPP - Editor Gráfico                                              | 48 |

|   |       | 4.1.2  | GPP - Editor de Texto                                             | 19 |

|   |       | 4.1.3  | GPP - Gerador de Código                                           | 50 |

|   | 4.2   | Virtuo | so                                                                | 50 |

|   |       | 4.2.1  | Tarefa                                                            | 51 |

|   |       | 4.2.2  | Semáforo                                                          | 51 |

|   |       | 4.2.3  | Caixa de Mensagem                                                 | 51 |

|   |       | 4.2.4  | Fila                                                              | 52 |

|   |       | 4.2.5  | Canais                                                            | 52 |

|   |       | 4.2.6  | Memória                                                           | 52 |

|   |       | 4.2.7  | Recursos                                                          | 53 |

|   |       | 4.2.8  | Temporizador                                                      | 53 |

|   | 4.3   | Cluste | r de DSPs Atlas                                                   | 53 |

|   | 4.4   | Kit XU | JP Virtex-II Pro                                                  | 54 |

|   | 4.5   | Consid | derações Finais                                                   | 57 |

| 5  | Trak   | palho Desenvolvido - Ambiente R-TEV                      | 58 |

|----|--------|----------------------------------------------------------|----|

|    | 5.1    | Visão Geral                                              | 58 |

|    | 5.2    | R-TEV - Reconfigurable Teaching Environment for Virtuoso | 59 |

|    | 5.3    | Manipulação de Componentes Reconfiguráveis com R-TEV     | 62 |

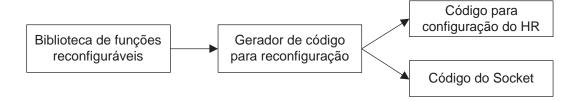

|    | 5.4    | Biblioteca de Funções Reconfiguráveis                    | 63 |

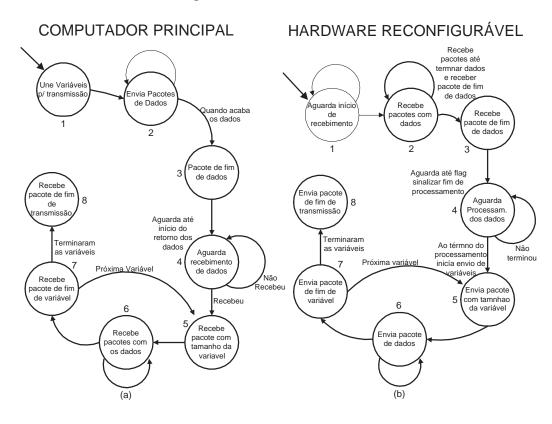

|    | 5.5    | Protocolo de Comunicação                                 | 64 |

|    | 5.6    | Socket                                                   | 68 |

|    | 5.7    | Geração de Código                                        | 69 |

|    | 5.8    | Desenvolvimento das Funções Reconfiguráveis              | 69 |

|    | 5.9    | Considerações Finais                                     | 70 |

| 6  | Estu   | do de Caso e Resultados Obtidos                          | 72 |

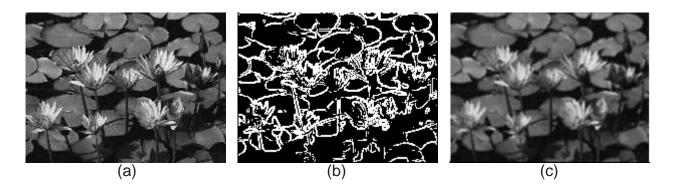

|    | 6.1    | Prewitt                                                  | 72 |

|    | 6.2    | Filtro Gaussiano                                         | 74 |

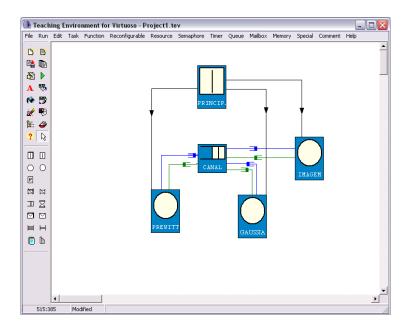

|    | 6.3    | O Desenvolvimento                                        | 75 |

|    | 6.4    | Resultados                                               | 76 |

|    | 6.5    | Implementação nos CLBs                                   | 77 |

|    |        | 6.5.1 VHDL para Prewitt                                  | 78 |

|    |        | 6.5.2 Prewitt SA-C                                       | 79 |

|    | 6.6    | Considerações Finais                                     | 79 |

| 7  | Con    | clusão e Trabalhos Futuros                               | 80 |

|    | 7.1    | Conclusão                                                | 80 |

|    | 7.2    | Trabalhos Futuros                                        | 81 |

| Re | eferên | cias                                                     | 82 |

| Ap | oêndio | ce A – Tutorial VHDL                                     | 88 |

| A.1     | INTRODUÇÃO                                       | 88 |

|---------|--------------------------------------------------|----|

|         | A.1.1 Origem                                     | 88 |

|         | A.1.2 Vantagens                                  | 38 |

|         | A.1.3 Desvantagens                               | 88 |

|         | A.1.4 Características                            | 39 |

|         | A.1.5 Níveis de Abstração                        | 39 |

| A.2     | COMENTÁRIOS E NOTAÇÕES NA LINGUAGEM VHDL         | 39 |

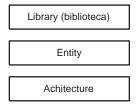

| A.3     | ESTRUTRURA DE UM PROGRAMA VHDL                   | 90 |

| A.4     | LIBRARY                                          | 90 |

| A.5     | ENTITY                                           | 90 |

| A.6     | ARCHITECTURE                                     | 91 |

| A.7     | DESCRIÇÃO DO COMPONENTE                          | 91 |

| A.8     | DESCRIÇÃO DO SINAL                               | 92 |

| A.9     | DESCRIÇAO DA LÓGICA                              | 92 |

| Apêndic | e B – Socket do Virtuoso                         | 95 |

| Apêndic | e C – Socket do Intermediário                    | 97 |

| Apêndic | e D – Socket do Hardware Reconfigurável          | 00 |

| Apêndic | e E – Código Fonte - Prewitt                     | 04 |

| Apêndic | Apêndice F – Código Fonte - Filtro Gaussiano 107 |    |

## Lista de Figuras

| 1  | Motivações para computação reconfigurável                                                                     | 15 |

|----|---------------------------------------------------------------------------------------------------------------|----|

| 2  | Computação Temporal (IDE, 2003)                                                                               | 19 |

| 3  | Computação Espacial (IDE, 2003)                                                                               | 19 |

| 4  | Comparação entre tipos de processadores                                                                       | 20 |

| 5  | Comparação entre <i>Binding Time</i> e Domínio Computacional (IDE, 2003)                                      | 22 |

| 6  | Comparação entre tamanho de instrução e tamanho de barramento (IDE, 2003) .                                   | 23 |

| 7  | Diagrama de custo do elemento lógico ao longo dos últimos anos                                                | 23 |

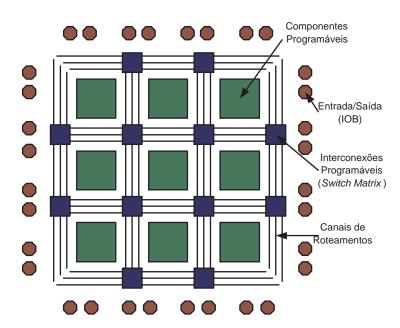

| 8  | Estrutura interna simplificada de uma FPGA                                                                    | 24 |

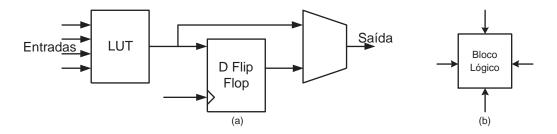

| 9  | (a) Bloco lógico típico de uma FPGA; (b) Disposição das entradas do bloco lógico                              | 25 |

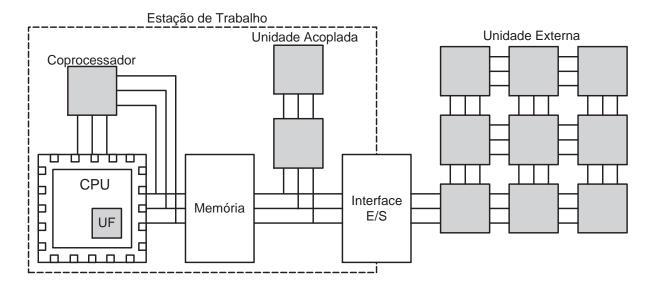

| 10 | Formas de Acoplamento do Hardware Reconfigurável                                                              | 26 |

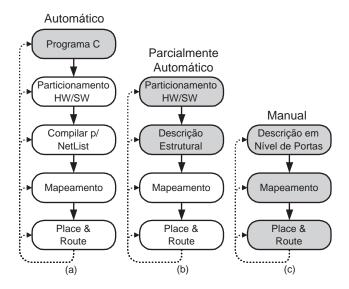

| 11 | Três fluxos possíveis para a implementação de um circuito em um sistema reconfigurável (COMPTON; HAUCK, 2002) | 31 |

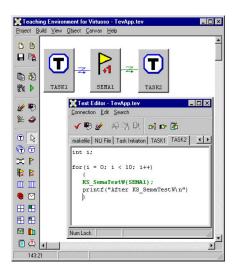

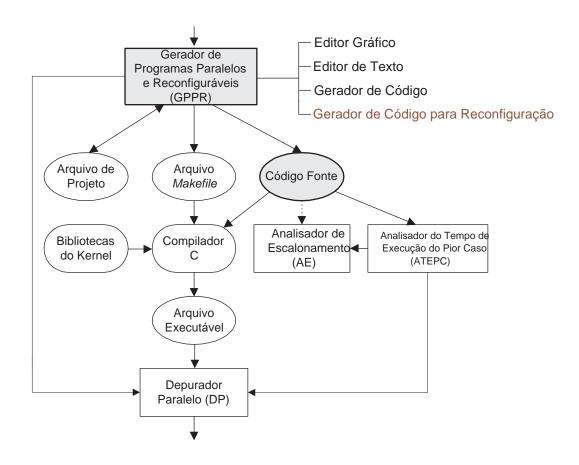

| 12 | TEV - Ambiente visual para o desenvolvimento de programas paralelos de tempo-real                             | 46 |

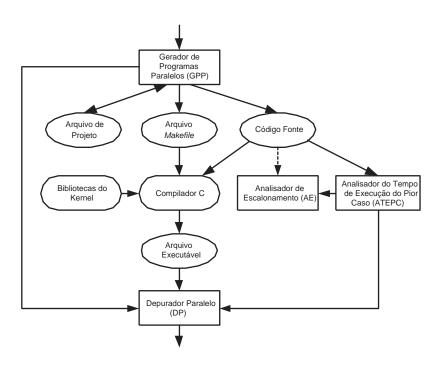

| 13 | Componentes do desenvolvimento de aplicações no TEV (RIBEIRO et al., 1998a)                                   | 47 |

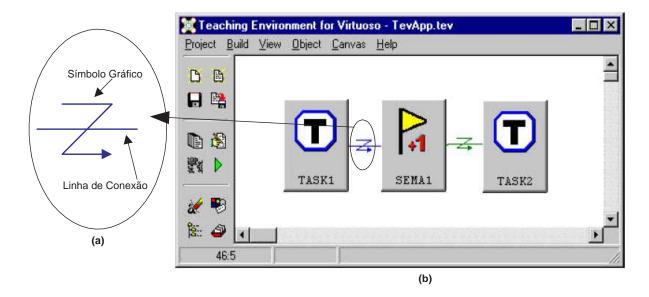

| 14 | Conexão entre duas tarefas                                                                                    | 49 |

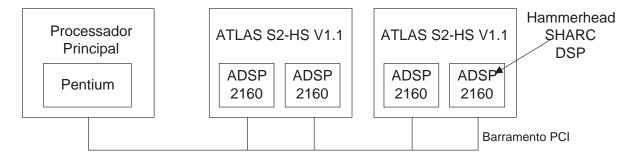

| 15 | Cluster de DSPs Atlas                                                                                         | 54 |

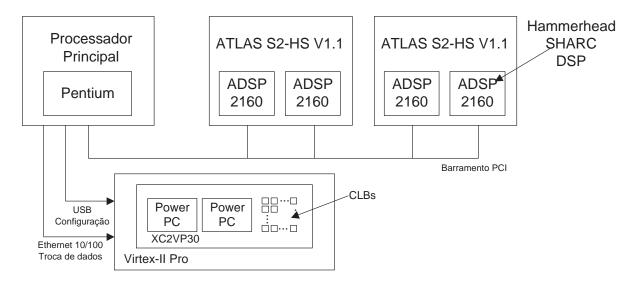

| 16 | Sistema ATLAS - Cluster de DSPs e processador principal                                                       | 54 |

| 17 | Kit XUP Virtex-II Pro                                                                                         | 55 |

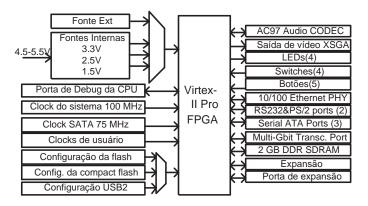

| 18 | Diagrama de blocos do Kit XUP (XILINX, 2006)                                                                  | 55 |

| 19 | Diagrama do FPGA Virtex-II Pro - XC2VP30 (XILINX, 2005c)                                                      | 56 |

| 20 | Componentes do desenvolvimento de aplicações no R-TEV                                                         | 61 |

| 21 | Geração de código reconfigurável realizada pelo GPPR                                                                                                                                  | 61 |

|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 22 | Sistema composto pelo ATLAS e XUP Virtex-II Pro                                                                                                                                       | 62 |

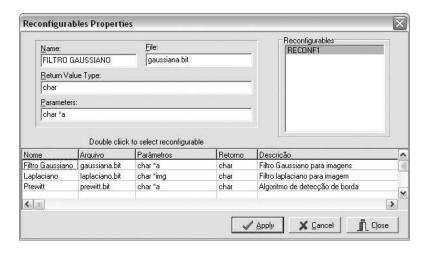

| 23 | Janela de Funções reconfiguráveis do R-TEV                                                                                                                                            | 63 |

| 24 | Arquivo descritor de função reconfiguráveis do R-TEV                                                                                                                                  | 64 |

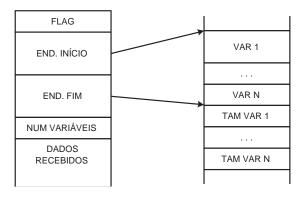

| 25 | Organização dos dados na memória DDR do HR                                                                                                                                            | 66 |

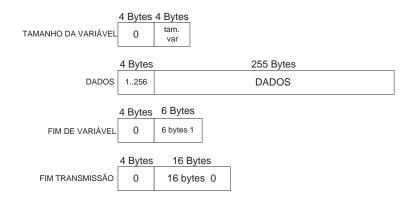

| 26 | Apresentação gráfica dos pacotes do socket                                                                                                                                            | 67 |

| 27 | Diagrama de estados do protocolo de comunicação para o computador principal (a) e o HR (b)                                                                                            | 67 |

| 28 | Máscaras (a) horizontal e (b) vertical                                                                                                                                                | 72 |

| 29 | Máscaras Gaussiana 3x3                                                                                                                                                                | 74 |

| 30 | Aplicação com as funções reconfiguráveis <i>Prewitt</i> e filtro <i>Gaussiano</i>                                                                                                     | 75 |

| 31 | Imagens Processadas: (a) Imagem original; (b) Filtro Prewitt; e (c) Filtro Gaussiano                                                                                                  | 76 |

| 32 | Estrutura de um programa em VHDL                                                                                                                                                      | 90 |

| 33 | Resultado da definição da interface através do exemplo de entity                                                                                                                      | 91 |

| 34 | Elementos da descrição de architecture                                                                                                                                                | 91 |

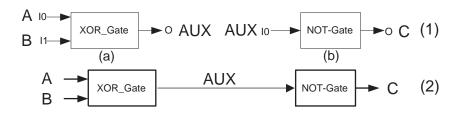

| 35 | Componentes a) XOR_Gate e b) NOT_Gate                                                                                                                                                 | 93 |

| 36 | Resultado do projeto usando a descrição estrutural: (1) asssociação dos sinais (port map) sobre os componentes usados; (2) interconexão dos componentes através dos sinais associados | 94 |

|    |                                                                                                                                                                                       |    |

## Lista de Tabelas

| 1 | Compiladores de propósito geral                            | 38 |

|---|------------------------------------------------------------|----|

| 2 | Valores do Flag                                            | 65 |

| 3 | Organização dos ponteiros de controle na memória DDR do HR | 65 |

| 4 | Descrição dos pacotes do socket                            | 66 |

| 5 | Resultados do Estudo de Caso                               | 77 |

## Resumo

Esta dissertação apresenta um ambiente para o desenvolvimento de aplicações reconfiguráveis em conjunto com o *kernel* de tempo real Virtuoso, denominado RTEV (*Reconfigurable Teaching Environment for Virtuoso*). Este tabalho é baseado no ambiente de desenvolvimento TEV (*Teaching Environment for Virtuoso*), desenvolvido no DC/UFSCar (Departamento de Computação da Universidade Federal de São Carlos). No ambiente RTEV é possível realizar o desenvolvimento de aplicações apenas selecionando uma função reconfigurável disponível na biblioteca de funções e realizar a interconexão com as demais funções da aplicação. Serão apresentados, para melhor entendimento: a computação reconfigurável; métodos de desenvolvimento de funções e/ou aplicações reconfiguráveis que podem ser utilizadas no desenvolvimento das funções da biblioteca reconfigurável; os sistemas utilizados no desenvolvimento; o ambiente RTEV; e um estudo de caso como validação da utilização do ambiente de desenvolvimento. Com este trabalho, busca-se simplificar e facilitar o acesso de programadores sem experiência em computação reconfigurável ao desenvolvimento de aplicações que fazem uso deste tipo de arquitetura.

## Abstract

This dissertation presents an environment for the development of reconfigurable applications, with Virtuoso Real-Time Kernel, called RTEV. This work is based on the TEV (Teaching Environment for Virtuoso), developed at DC/UFSCar (Department of Computation of the Federal University of Sao Carlos). In RTEV, it is possible to carry through the development of applications only selecting a reconfigurable function from the library of available functions and making the interconnections with other functions of the applications. It will be presented, for better understanding: a reconfigurable computer review; development methods of functions and/or applications that can be used for the construction of the reconfigurable library; the systems used in the development environment RTEV; and a case study as a way of validation of the development environment. This environment allows the programmers, without any reconfigurable hardware knowledge, to develop applications with reconfigurable components.

## 1 Introdução

Neste capítulo serão apresentadas a motivação e relevância para este trabalho, definição do problema e dos objetivos. E será apresentada a estrutura do texto.

## 1.1 Motivação e Relevância

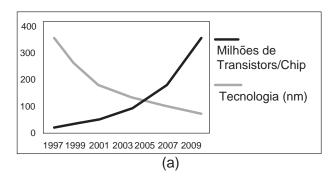

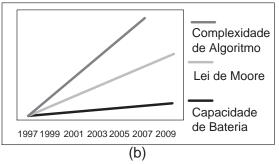

O aumento constante na densidade de transistores dos *chips*, tanto para uso geral quanto para sistemas embarcados, é propiciado pela melhoria da tecnologia de produção. Porém, isso faz com que os chips fiquem cada vez mais sofisticados e de custo elevado. A Figura 1a apresenta o gráfico de crescimento da quantidade de transistores (em milhões) por *chip* comparado com a melhoria na tecnologia de fabricação, diminuindo a dimensão de um transistor em nm (nano-metros), ilustrando a afirmação anterior. Além disso o aumento da complexidade dos algoritmos, requerendo cada vez maior densidade de transistores para realizar os cômputos em tempo satisfatório, execede a *lei de Moore*. Segundo a lei de Moore, a cada 18 meses a integraçã dos circuitos dos computadores dobra, enquanto os custos permanecem constantes. Por outro lado, o aumento da capacidade de processamento exigido pelo aumento da complexidade dos algoritmos esbarra no baixo crescimento da capacidade das baterias dos sistemas, principalmente em sistemas embarcados. Cria-se assim uma severa limitação de consumo de energia, nos sistemas embarcados onde este tipo de problema é crítico. A Figura 1b mostra a taxa de crescimento para a complexidade dos algoritmos, para a tecnologia de computadores (Lei de Moore) e a capacidade de bateria.

Esses problemas dificilmente serão satisfeitos pelos processadores tradicionais nos próximos anos. Uma alternativa aos processadores tradicionais são os computadores, ou arquiteturas, reconfiguráveis. A principal característica dos sistemas reconfiguráveis é a possibilidade de se configurar, ou utilizar, diversos circuitos diferentes, em um único *hardware* reconfigurável. Com isso, supera-se os problemas de necessidade de aumento de quantidade de transistores e consequentemente de consumo de energia, ampliando, desta forma, o leque de aplicações com uma tecnologia de circuitos reconfiguráveis disponível no mercado.

Figura 1: Motivações para computação reconfigurável

A constante evolução no desenvolvimento da computação reconfigurável e consequentemente sua maior utilização em sistemas computacionais convencionais, vem apresentando resultados que demonstram o potencial de tal arquitetura e sua viabilidade de projeto, implementação e utilização (DEHON, 2000).

O projeto de aplicações para este tipo de arquitetura requer grande conhecimento e especialização, sendo necessário que o desenvolvedor, além de conhecer bem a aplicação tenha um profundo e detalhado conhecimento da arquitetura reconfigurável específica para a sua aplicação. Devido a esta dificuldade de desenvolvimento e, principalmente, a dificuldade de integração e inclusão de sistemas reconfiguráveis em sistemas convencionais, os desenvolvedores costumam não fazer uso deste tipo de computação.

Um grande número de metodologias, *frameworks*, linguagens e extensões de linguagens tem sido disponibilizado para auxiliar e simplificar o desenvolvimento de aplicações reconfiguráveis. Entretanto, a integração do hardware reconfigurável com sistemas convencionais ainda é complexa. A razão principal é que não é trivial, para desenvolvedores que não possuem conhecimento em computação reconfigurável, a implementação de interação entre os sistemas convencional e reconfigurável ou protocolos de comunicação.

Este trabalho apresenta um ambiente de desenvolvimento amigável para aplicações reconfiguráveis, tornando o hardware reconfigurável quase transparente ao programador. O sistema proposto permite ao programador, sem qualquer conhecimento de hardware reconfigurável, desenvolver aplicações utilizando componentes reconfiguráveis.

O desenvolvimento consistiu em integrar a programação de hardware reconfigurável no TEV (Teaching Environment for Virtuoso), um ambiente visual para o desenvolvimento de aplicações paralelas de tempo real, desenvolvido no Departamento de Computação da Universidade Federal de São Carlos (DC/UFSCar) (MORóN et al., 2000), para o sistema operacional de tempo real Virtuoso (WIND, 2001). TEV é um ambiente que permite desenvolver aplicações paralelas

de tempo real simplesmente utilizando grafos, com nós representando as funções e linhas denotando a comunicação entre as funções. O sistema proposto é chamado R-TEV (*Reconfigurable-TEV*). Como estudo de caso do R-TEV, é utilizada uma placa XUP (Xilinx University Program) com um FPGA (Field Programmable Gate Array) Virtex-II Pro XC2VP30.

Sendo assim, a motivação deste trabalho é possibilitar o desenvolvimento de aplicações para computadores reconfiguráveis pelos programadores sem conhecimentos específicos deste tipo de arquitetura, explorando diversas formas de processamento, principalmente paralela de granulosidade fina.

## 1.2 Objetivos e Definição do Problema

O objetivo deste trabalho é a implementação de um ambiente de desenvolvimento de aplicações utilizando computações reconfiguráveis. Esse ambiente permite a um projetista realizar o desenvolvimento de aplicações apenas escolhendo os recursos disponibilizados de computação reconfigurável e realizando a interconexão com as demais funções.

No entanto, é necessário que as funções reconfiguráveis tenham sido desenvolvidas previamente e disponibilizadas na biblioteca reconfigurável, composta por um conjunto de funções reconfiguráveis.

## 1.3 Estrutura do Texto da Dissertação

A presente descrição está dividida em 7 partes além das referências bibliográficas e apêndices:

- Capítulo 1 Apresenta a motivação e relevância do trabalho, assim como, os objetivos e definição do problema.

- Capítulo 2 Apresenta uma revisão sobre as arquiteturas reconfiguráveis, mostrando suas características e motivos pelo qual optamos por este tipo de arquitetura.

- Capítulo 3 Apresenta diversas metodologias para o desenvolvimento de aplicações reconfiguráveis, mostra a ampla gama de possibilidades existentes para o desenvolvimento dos mais variados tipos de aplicações.

- Capítulo 4 Apresenta os sistemas utilizados no desenvolvimento. Apresenta o ambiente

TEV Teaching Environment for Virtuoso, o Kernel Virtuoso, Cluster de DSPs Atlas

- e a placa de desenvolvimento de aplicações reconfiguráveis XUP (*Xilinx University Program*) Virtex-II Pro, dando uma visão geral de suas estruturas, funcionamento e potencial.

- Capítulo 5 Apresenta o trabalho desenvolvido e a sua implementação com a adaptação do ambiente de desenvolvimento TEV para o desenvolvimento de aplicações utilizandose funções reconfiguráveis. Apresenta também o trabalho realizado, detalhando cada etapa.

- Capítulo 6 Apresenta um estudo de caso utilizando o ambiente R-TEV.

- Capítulo 7 Conclusões e Proposições Futuras.

## 2 Revisão Sobre Arquiteturas Reconfiguráveis

No início da década de 1980, surgiram os primeiros circuitos FPGAs (*Field Programmable Gate Array*), componentes reconfiguráveis, inicialmente utilizados para facilitar o desenvolvimento de protótipos de circuitos, devido à sua flexibilidade. Posteriormente, esses circuitos começaram a ser utilizados para aumentar o desempenho de processamento, diminuindo a barreira entre hardware e software, com a implementação diretamente em Hardware (HW) de algoritmos que têm baixo desempenho em Software (SW).

As arquiteturas de computador que fazem uso deste tipo de circuitos e de suas características de reconfiguração são denominadas arquiteturas reconfiguráveis que serão apresentadas neste capítulo.

As duas primeiras seções deste capítulo apresentam algumas características de grande relevância, como tolerância a falhas e prototipagem rápida. Na seqüência, mostram-se as diferenças entre a computação temporal e a computação espacial, e os tipos de computações quanto ao seu tempo de programação e área de implementação utilizada. Apresenta-se ainda a evolução do custo dos elementos lógicos e a possibilidade de reconfiguração parcial e dinâmica.

### 2.1 Hardware X Software

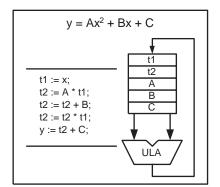

Os processadores de propósito geral (microprocessadores) utilizados em computadores pessoais (PCs) são capazes de resolver qualquer tipo de computação, utilizando diferentes programas (SW), cada qual com seu propósito específico. Este tipo de computação é conhecido como computação temporal ou software/temporal, em que os elementos de processamento são distribuídos no tempo, isto é, há um pequeno número de blocos de processamento genéricos que são reutilizados várias vezes no tempo. Na Figura 2, é apresentado um exemplo de computação temporal em que se calcula uma expressão aritmética  $Ax^2 + Bx + C$  e posteriormente atribui-se o resultado à variável y. A expressão é calculada sequencialmente utilizando variáveis tem-

porárias  $t_1$  e  $t_2$ . Inicialmente,  $t_1$  recebe o valor  $x(t_1 := x)$ ; em seguida  $t_2$  recebe  $A * t_1$ ; seguido de  $t_2 + B$  e  $t_2 * t_1$ ; finalmente, y recebe  $t_2 + C$ . Os valores A, B, C,  $t_1$  e  $t_2$  são variáveis contidas em registradores e os cálculos são realizados através de uma única ULA (Unidade Lógica e Aritmética). Na grande maioria das aplicações computacionais, este tipo de processador é a solução mais simples e oferece ótimos resultados de custo/benefício. Apresenta facilidade e rapidez no desenvolvimento de aplicações, devido ao uso de linguagens de alto nível.

Este tipo de processador possui uma gama muito grande de microinstruções disponíveis, para os mais variados tipos de aplicação, bem como o HW necessário para realizar todas as execuções de forma sequencial. Em contrapartida, na maior parte do tempo apenas uma pequena porção dos recursos disponíveis está sendo utilizado, levando a um desperdício de recursos e baixando a eficiência.

De lado oposto temos os processadores e circuitos específicos para determinadas aplicações conhecidos como ASICs (*Application Specific Integrated Circuit*). Esses processadores são desenvolvidos para aplicações que necessitam de certas características que não são tipícas dos processadores de propósito geral, tais como alta velocidade de processamento, baixo consumo de energia, pequena dissipação de calor, tamanho reduzido e baixo custo.

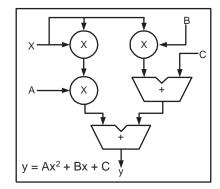

ASICs são compostos de circuitos específicos desenvolvidos em hardware que executam de forma espacial o cômputo, ou seja, cada operador lógico/aritmético se encontra em uma determinada posição no espaço, configurando a aplicação. Este tipo de computação, conhecida como hardware/espacial (DEHON, 1996) (MIRSKY, 1996), permite a exploração mais eficiente do paralelismo de dados, a fim de obter maior desempenho e menor latência, como ilustrado na Figura 3. Nessa figura é possível verificar o mesmo cálculo mostrado na Figura 2 realizado espacialmente, em paralelo, utilizando 3 multiplicadores e dois somadores dispostos espacialmente.

Figura 2: Computação Temporal (IDE, 2003) Figura 3: Computação Espacial (IDE, 2003)

Devido às características e especificidades de cada aplicação, o desenvolvimento de com-

putadores específicos para cada uma delas é, em geral, complexo e caro, demandando mão de obra muito especializada e tempo de desenvolvimento e custo elevados.

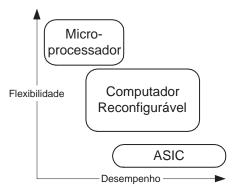

Como já citado na introdução, os FPGAs tornaram possível os Processadores Reconfiguráveis que cobrem o espaço intermediário entre os dois tipos de processadores. A Figura 4 apresenta um gráfico onde se verifica a situação de cada um dos processadores no espaço desempenho versus flexibilidade. As arquiteturas reconfiguráveis tendem a fazer uso da computação espacial, para aplicações específicas, implementando em HW aplicações que possuem baixo desempenho em SW. Além disso possuem flexibilidade para criação de aplicações diversas, utilizando um mesmo chip, e desenvolvimento mais simples, rápido e de custo menor em relação aos ASICs.

Figura 4: Comparação entre tipos de processadores

## 2.2 Vantagens da Reconfiguração

#### 2.2.1 Tolerância a Falhas

Em um sistema computacional composto por um conjunto de unidades de processamento, o tratamento de possíveis falhas é necessário. Esta é uma outra área onde a computação reconfigurável tem sido aplicada. Sistemas tolerantes a falhas reconfiguráveis são capazes de inutilizar a área defeituosa e corrigi-la, enquanto o restante do sistema continua em operação. Já uma falha detectada em arquiteturas convencionais, implementadas em Circuitos Integrados(CI) não-reconfiguráveis, implica em inutilização completa dos CIs (MESQUITA, 2002).

### 2.2.2 Prototipagem Rápida

Alterando-se os dados de reconfiguração de um circuito integrado FPGA é possível programar os componentes e a fiação necessária para interconexão entre os blocos lógicos internos. O

tempo de implementação de um protótipo para uma dada aplicação é bastante curto, consistindo basicamente no tempo de projeto usando algum ambiente de desenvolvimento. Essa é uma clara distinção em relação aos projetos convencionais de VLSI (*Very Large Scale Integration*), onde decorrem muitas semanas entre o projeto e a implementação real devido à necessidade de fabricação do circuito, incluindo todos os processos de microeletrônica, até o encapsulamento final. Esta característica de FPGAs cria oportunidade para novas metodologias de projeto.

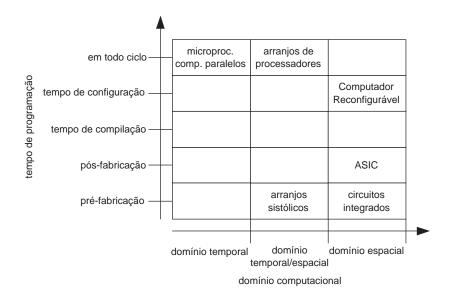

#### 2.2.3 Tempo de Programação

O tempo de programação, ou Binding Time, é uma característica importante para a distinção dos três tipos de computação: (a) hardware/espacial; (b) software/temporal; e (c) reconfigurável. No caso de circuitos integrados convencionais, a programação e a interconexão dos dispositivos são feitas antes e durante o processo de fabricação respectivamente, sob especificação do fabricante. Os componentes ASIC's, que são circuitos integrados específicos para cada aplicação, são programados sob especificação do usuário; entretanto esta programação é fixa e pós-fabricação. Microprocessadores convencionais necessitam de busca/decodificação e execução de instruções da memória a cada ciclo e, portanto, a programação do circuito para a execução de instruções é feita em todos os ciclos. No presente contexto, entende-se como programação o ato de especificar a forma de funcionamento para o circuito. Já em arquiteturas reconfiguráveis, a configuração do dipositivo é programável, através de bits de seleção de contexto, ou "instrução". Cada bit da "instrução" corresponde à função de um determinado operador da arquitetura (DEHON; WAWRZYNEK, 1999). A Figura 5 mostra a distribuição desses modelos de arquitetura de acordo com seu tempo de programação, momento em que ocorre a programação do componente e domínio computacional, sistemas com computação puramente temporal, parte temporal e parte espacial e puramente espacial (HARTENTEIN, 2001). Incluemse também nessa figura os arranjos de processadores convencionais e os arranjos sistólicos, que são arranjos de pequenos processadores que funcionam sincronamente para o processamento vetorial.

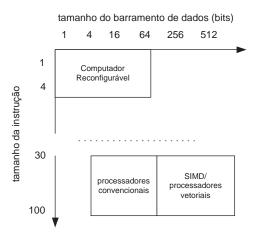

## 2.2.4 Área

O tipo de "instrução" praticamente define/distingue dispositivos configurados pós-fabricação. Arquiteturas convencionais utilizam um conjunto de instruções fixas, normalmente 32/64 bits, que definem o funcionamento do fluxo de dados; já arquiteturas reconfiguráveis muitas vezes são compostas por um conjunto de operadores aritméticos unários, cujo controle é feito por apenas um bit de configuração. Durante o projeto de processadores a área de silício ocupada

Figura 5: Comparação entre *Binding Time* e Domínio Computacional (IDE, 2003)

é basicamente definida por:

- tamanho do barramento de dados; e

- tamanho da instrução.

Nas instruções de processadores convencionais todos os bits de uma determinada instrução devem obrigatoriamente executar/participar da mesma operação, em cada ciclo, sejam dados manipulados da memória ou de registradores. Em componentes ASIC's é possível projetar um barramento de dados e tamanho de instrução coerente com o tipo de aplicação. Por outro lado, em computadores de propósito geral existe a preocupação de que o *chip* deve tanto suportar computações de granularidade grossa (mais adiante neste capítulo sera discutido a granulosidade de unidades computacionais), como pequenos cálculos aritméticos. Neste ponto, cada instrução é maior ou igual ao tamanho máximo que cada ULA suporta.

Circuitos reconfiguráveis baseados em FPGA's podem ser comparados com computadores que manipulam instruções simples de um bit, o que resulta em baixo *overhead* de processamento, pois o tamanho do circuito necessário para cada instrução é sempre ajustado para o tamanho ótimo para o cômputo. Assim a quantidade de circuitos para instruções é minimizada, aumentando a capacidade do *chip* para novos tipos de computação. Isto pode ser creditado à economia de espaço por adequar o tamanho de implementação de instruções, barramento e unidades à necessidade específica de cada aplicação, utilizando somente os bits necessários para cada instrução.

A Figura 6 ilustra um comparativo da relação do tamanho da instrução com o tamanho do barramento. Nota-se que os circuitos reconfiguráveis conseguem operar sobre um mesmo tamanho de barramento que processadores convencionais, utilizando um tamanho reduzido de instruções (DEHON; WAWRZYNEK, 1999)

Figura 6: Comparação entre tamanho de instrução e tamanho de barramento (IDE, 2003)

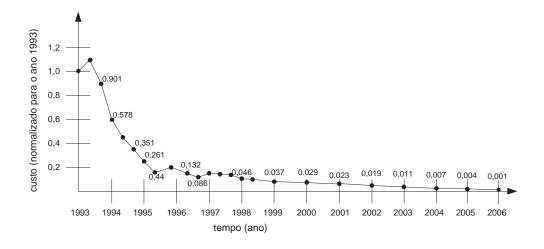

#### 2.2.5 Custo Financeiro

O principal componente de uma arquitetura reconfigurável, sem dúvida, é o FPGA: os elementos lógicos que o compõem são combinados de forma a se obter o desempenho desejado. Nota-se na Figura 7 (ALTERA, 2006a) que, de 1993 até os dias atuais o custo por elemento lógico, de um FPGA, vem sofrendo uma constante queda, cerca de 40% por ano e ao mesmo tempo, há um crescente aumento da quantidade de unidades lógicas por área.

Figura 7: Diagrama de custo do elemento lógico ao longo dos últimos anos

#### 2.2.6 Reconfiguração Parcial/Dinâmica

Os FPGA's mais modernos possuem a característica de reconfiguração em tempo real. Esta propriedade permite que, enquanto parte do sistema está em processamento, uma outra parte pode estar sendo reconfigurada para executar outro conjunto de instruções. Dessa forma, também é possível a reutilização de *hardware*, contribuindo para economia de recursos computacionais (MESQUITA, 2002).

#### 2.3 FPGA

FPGA é um dispositivo que possui componentes lógicos programáveis (blocos lógicos) e interconexões programáveis (Switch Matrix) que podem ser configurados de acordo com as aplicações do usuário (programador). Os componentes programáveis podem ser programados de forma a se comportar como portas lógicas básicas (como E, OU, NÃO, OU-EXCLUSIVO) ou funções combinatórias mais complexas como decodificadores ou funções matemáticas simples. Na maioria dos FPGAs estes componentes programáveis podem ser elementos de memórias, que podem ser simples *flip-flops* ou blocos de memórias completos, multiplicadores ou funções mais avançadas. Os FPGAs são compostos ainda por blocos de entrada e saída (IOB - *Input Output Block*) que são responsáveis pelo interfaceamento com componentes externos. Os blocos lógicos são dispostos em forma bidimensional, e os canais de roteamento interligam as interconexões programáveis em formas de trilhas verticais e horizontais entre as linhas e as colunas dos blocos lógicos conforme mostra a Figura 8.

Figura 8: Estrutura interna simplificada de uma FPGA

Um bloco lógico típico de um FPGA é composto por uma *lookup table* (LUT) de 4 entradas, e um *flip-flop* tipo D como mostrado na Figura 9a. Há apenas uma saída, que pode ser registrada (fazendo uso de registrador) ou não-registrada. Cada bloco lógico tem quatro entradas para LUT e um ciclo de do relógio (clock), estando cada entrada disposta em um lado do bloco permitindo que este se conecte com seus quatro vizinhos (Figura 9b).

Figura 9: (a) Bloco lógico típico de uma FPGA; (b) Disposição das entradas do bloco lógico

FPGAs modernos expandiram suas capacidades e incluíram funcionalidades de alto nível implementadas diretamente em HW. Com essas funcionalidades embarcadas reduz-se a área utilizada e a complexidade de desenvolvimento das aplicações e aumenta-se o desempenho. Como exemplos pode-se citar multiplicadores, aritmética de ponto flutuante, blocos genéricos de DSP, processadores, E/S de alta velocidade e memória interna.

## 2.4 Características e definições de arquiteturas reconfiguráveis

Existem vários tipos diferentes de arquiteturas reconfiguráveis. Para classificá-los devemos considerar tanto o paradigma de *hardware* como de *software*. São apresentadas a seguir algumas características relevantes para definição e entendimento dos mais variados tipos de arquiteturas reconfiguráveis.

#### 2.4.1 Acoplamento

Uma das principais diferenças entre as arquiteturas reconfiguráveis é o grau de acoplamento das unidades reconfiguráveis com o processador principal. Como certos tipos de operações não são muito eficientes em lógica programável, como por exemplo laços, saltos, desvios e E/S, os processadores reconfiguráveis estão geralmente acoplados a um microprocessador que fica responsável por executar tais tarefas. Podemos diferenciar o grau de acoplamento em quatro níveis (HAUCK, 1998) (COMPTON; HAUCK, 2000). A Figura 10 mostra os diferentes níveis de

acoplamento de unidades reconfiguráveis em destaque, quais sejam: UF (unidade funcional), coprocessador, unidade acoplada e unidade externa.

Figura 10: Formas de Acoplamento do Hardware Reconfigurável

No primeiro nível, o hardware reconfigurável é utilizado apenas como uma unidade funcional do processador principal. Assim, permite-se uma programação tradicional com a adição de instruções específicas que podem ser alteradas conforme a necessidade. Aqui, a unidade reconfigurável é executada utilizando o barramento principal do processador principal, com registradores usados para guardar operandos de entrada e saída.

No segundo nível, a unidade reconfigurável é utilizada como um coprocessador. Um coprocessador é, em geral, maior que uma unidade funcional e realiza o cômputo sem supervisão constante do processador principal. O processador principal inicializa a reconfiguração e envia os dados ou provê informação de onde os dados estão na memória.

No terceiro nível, uma unidade de reconfiguração comporta-se como um processador em um sistema multiprocessado. O *cache* de dados do processador principal não pode ser acessado diretamente pelo processador reconfigurável. Neste caso há um atraso maior na comunicação entre os processadores. Entretanto, este tipo de hardware reconfigurável permite uma ampla gama de processamento independente, enviando o resultado de uma grande quantidade de processamento de uma única vez para o processador principal.

Finalmente, o mais fracamente acoplado dos processadores reconfiguráveis são as unidades de processamento externas (*stand-alone*). Este tipo de hardware reconfigurável possui pouca comunicação com o processador principal, devido ao alto custo de comunicação. Este modelo é similar a estações de redes, onde o processamento ocorre por um longo período de tempo, sem muita comunicação.

Cada um destes tipos de acoplamento tem suas vantagens e desvantagens. Quanto mais integrado o *hardware* reconfigurável estiver com o processador principal, com mais frequência poderá ser solicitado para computações menores, devido ao baixo custo de comunicação. Entretanto, o *hardware* é incapaz de processar por longo período de tempo sem a intervenção do processador principal, pois utiliza recursos deste, e a lógica reconfigurável disponível, geralmente, é um tanto limitada. Quanto mais distante estiver do processador maior será a capacidade de execução autônoma. Entretanto, em aplicações que possuem um alto custo de comunicação, o ganho pode ser reduzido ou até mesmo ultrapassado pelo atraso na comunicação.

#### 2.4.2 Granulosidade

Além do nível de acoplamento, pode-se variar o tamanho dos blocos lógicos. Cada unidade computacional, ou bloco lógico, pode variar desde uma simples porta lógica de 3 entradas a uma complexa ULA (Unidade Lógica e Aritmética). Esta diferença de tamanhos é classificada como granulosidade do sistema e pode ser fina, média ou grossa.

**Grão Fino**: Blocos lógicos de grão fino são normalmente constituídos por portas lógicas e multiplexadores. São geralmente utilizados para manipulação em nível de bit, e são frequentemente encontradas em aplicações de criptografia e processamento de imagens. Além disso, permitem um grande potencial de exploração do paralelismo da aplicação e flexibilidade. Entretanto, o *overhead* de comunicação, devido à grande quantidade de blocos, pode ser um ponto crítico.

**Grão Médio**: Intermediário entre o grão fino e grosso, é utilizado em grande parte de sistemas reconfiguráveis. É capaz de executar um conjunto de instruções por ciclo e provê estruturas computacionais mais eficientes para problemas mais complexos, como por exemplo máquinas de estados finitos. Em geral utiliza duas ou mais palavras de 4-bits.

**Grão Grosso**: São blocos lógicos grandes e complexos, otimizados para grandes cômputos, capazes de executar programas inteiros em poucos ciclos. Devido à otimização destes blocos para computações grandes, obtém melhores resultados (e utilizam menor área em chip) do que um conjunto de pequenas células conectadas formando o mesmo tipo de estrutura. Entretanto, devido à sua composição estática, são incapazes de realizar otimizações no tamanho dos operandos.

#### 2.4.3 Capacidade de Reconfiguração

O sistemas reconfiguráveis podem diferir também de acordo com o momento, a quantidade de vezes e como ocorrem as configurações. Quanto à forma de reconfiguração, os sistemas podem ser divididos em 4 grupos (COMPTON; HAUCK, 2002):

**Estático**: O sistema é configurado uma única vez e nunca é modificado. O dispositivo é programado para executar uma determinada função e não é alterado durante toda a vida útil do sistema. Este grupo não tira vantagem da flexibilidade provida pela reconfiguração, utilizase apenas da facilidade de desenvolvimento de circuitos utilizando-se componentes reconfiguraçeis.

**Estaticamente Reconfigurável**: O sistema é reconfigurado várias vezes, para várias funções diferentes, mas as reconfigurações ocorrem sempre ao fim completo de um processamento. Estes sistemas tiram proveito das características reconfiguráveis do componente para execução de diferentes tarefas em um mesmo HW.

**Dinamicamente Reconfigurável**: Estes sistemas aproveitam completamente as características dos componentes reconfiguráveis, alterando ou reconfigurando as funções em tempo de execução. Este tipo de reconfiguração acarreta um *overhead* de reconfiguração que deve ser muito bem analisado para não comprometer o desempenho final do sistema.

Parcial e Dinamicamente Reconfigurável: Neste tipo de sistema, apenas uma parte do componente reconfigurável é alterada em tempo de execução. Nem todos os dispositivos reconfiguráveis suportam tal tipo de reconfiguração. Este tipo de sistema apresenta, em geral, um desenvolvimento de aplicação muito complexo e necessita de um profundo conhecimento tanto do dispositivo quanto da aplicação. A reconfiguração parcial é muito utilizada para correção de falhas, sistemas evolutivos e para minimizar o *overhead* de reconfiguração dos sistemas dinamicamente reconfiguráveis.

A opção por um destes quatro tipos de modos de reconfiguração deve ser definida de acordo com as caracteristícas e necessidades de desempenho, custo e disponibilidade que o sistema necessita.

## 2.5 Considerações Finais

As características e classificações apresentadas neste capítulo têm o objetivo de apresentar as arquiteturas reconfiguráveis e mostrar o quão válida é a sua utilização. A constante utilização destes componentes e os problemas por estes solucionados, motivaram o estudo e utilização

de FPGA's em implementação de computadores. Como pode ser notado, os sistemas reconfiguráveis são complexos e seu projeto é trabalhoso e custoso, pequenos detalhes podem alterar completamente as características e, até mesmo, comprometer o funcionamento de um sistema. Porém, esses sistemas são mais flexíveis para a criação de aplicações espaciais, utilizando um mesmo chip e apresentam uma característica de desenvolvimento mais simples, rápida e de custo menor em relação aos ASICs.

Das características apresentadas, destacam-se: prototipagem rápida, computação espacial, flexibilidade, baixo custo e a possibilidade de reconfiguração parcial/dinâmica.

# 3 Abordagens para o Desenvolvimento de Aplicações Usando Arquiteturas Reconfiguráveis

Apesar de os sistemas reconfiguráveis terem desempenho significantemente melhor em relação a sistemas convencionais e trazerem muitos benefícios, geralmente, são ignorados pelos programadores e desenvolvedores devido à complexidade de desenvolvimento de aplicações. A menos que haja uma maneira fácil de desenvolvimento dos sistemas reconfiguráveis, essa situação continua requerendo ambientes de desenvolvimento que auxiliem na criação de configurações e na inserção e interação com os sistemas convencionais. Estes ambientes podem variar de simples assistentes para projetos manuais de circuitos reconfiguráveis, a sistemas automáticos completos desses projetos.

## 3.1 Uma visão geral

O projeto manual de circuitos reconfiguráveis, além de moroso, requer um grande conhecimento do sistema reconfigurável para o qual será destinado, além de moroso. Por outro lado, o sistema automático é um meio rápido e fácil para criar configurações para sistemas reconfiguráveis torna tal tipo de desenvolvimento mais acessível, embora nem sempre gera a melhor solução para o problema.

Os desenvolvimentos precisam passar por diversas fases como ilustra a Figura 11, onde são apresentadas três formas de desenvolvimento de projetos de reconfiguração: (a) automático, (b) parcialmente automático e (c) manual. As etapas em cinza são realizadas manualmente pelo desenvolvedor, enquanto as etapas em branco são realizadas automaticamente. As linhas pontilhadas representam trajetos para melhorar o circuito resultante. No sistema automático o programa C é particionado em *hardware* e *software* e então, são gerados e compilados para *NetList* (lista de componentes no nível de portas lógicas), que é mapeado para o *hardware*; então, realiza-se o *Place & Route* (posicionamento e interligação dos componentes reconfig-

uráveis). No sistema parciamente automático, o usuário realiza o particionamento em *hardware* e *software*, descreve estruturalmente o *hardware*, então realiza-se o mapeamento e o *Place & Route*. No sistema manual é realizada a descrição do *hardware* em nível de portas lógicas, que são mapeadas para o *hardware* e realiza-se entao o *Place & Route*.

Figura 11: Três fluxos possíveis para a implementação de um circuito em um sistema reconfigurável (COMPTON; HAUCK, 2002)

A descrição do circuito é o processo que descreve as funções a serem colocadas no *hard-ware* reconfigurável. Isto pode ser feito de maneira simples, escrevendo um programa em linguagem de alto nível como C, que representa a funcionalidade do algoritmo a ser executado. Por outro lado, pode ser complexo, realizando a descrição das entradas, saídas e operações de cada bloco básico do sistema reconfigurável. Entre os dois extremos pode-se descrever o circuito utilizando-se componentes genéricos complexos, como somadores ou multiplicadores que serão especifícados no *hardware* reconfigurável em outra etapa do processo.

Para descrições em linguagem de alto nível, como C/C++ ou Java, ou outra que utiliza blocos lógicos complexos, o código deve ser compilado em uma rede (*netlist*) de componentes em nível de portas lógicas. A implementação em linguagens de alto nível envolve a geração dos componentes para realizar as operações aritméticas e lógicas, e separadamente as estruturas de controle do programa, como laços e operações de salto. Cada descrição estrutural, gerada por uma linguagem de alto nível ou especificada manualmente pelo usuário, ou seja, cada estrutura complexa, deve ser substituída por uma rede de portas lógicas equivalentes.

Uma vez detalhado no nível de portas ou elementos lógicos, o circuito está criado. Estas estruturas devem, agora, ser convertidas aos elementos reais da lógica do *hardware* reconfigurável para o qual são desenvolvidas. Este estágio é chamado de Mapeamento, e é dependente

da arquitetura do *hardware* utilizado. Para arquiteturas baseadas em LUTs, esta etapa divide o circuito em pequenas subfunções, que possam ser mapeadas em uma única LUT (BROWN et al., 1992a) (ABOUZEID et al., 1993) (CHANG et al., 1996) (HAUCK; AGARWAL, 1996) (LIN et al., 1997) (CONG; WU, 1998) (TOGAWA et al., 1998) (CONG et al., 1999).

Depois de descrito o circuito, os blocos resultantes devem ser configurados no *hardware* reconfigurável. Cada um destes blocos deve ser colocado em uma posição específica dentro do *hardware*, sendo que esta posição deve ser a mais próxima possível aos blocos com os quais se comunica. Quanto maior for a capacidade das FPGAs, maior é o tempo gasto nesta fase de disposição (*Place & Route*). *Foorplanning* é uma técnica que pode ser usada para diminuir esse tempo. O algoritmo de *foorplanning* primeiro divide as células lógicas em conjuntos, onde as células com grande quantidade de comunicação são agrupadas. Estes conjuntos são então colocados como unidades em regiões do *hardware* reconfigurável. Uma vez realizada a disposição global, o algoritmo de posicionamento realiza o posicionamento detalhado dos blocos lógicos individuais dentro dos limites atribuídos ao conjunto (SANKAR; ROSE, 1999).

Após o *foorplanning*, os blocos lógicos individuais são colocados em células lógicas específicas. Um algoritmo que é geralmente utilizado é a técnica de *simulated annealing* (KRUP-NOVA et al., 1997) (SENOUCI et al., 1998). Este método realiza uma disposição inicial (pseudo-) aleatória, e então executa uma série de "movimentos" nesta disposição. Um movimento é simplesmente a mudança de localização de uma célula lógica ou a troca de posição entre duas células. Estes movimentos são realizados um a um utilizando alvos aleatórios. Caso o movimento melhore a disposição, então a mesma é alterada. Movimentos indesejados são aceitos em uma pequena porcentagem das vezes, o que ajuda a evitar desperdício de pequenos locais dentro da disposição. Existem outros algoritmos que não se baseiam em movimentos aleatórios (GEHRING, 1996), que buscam a minimização de área utilizada, o que nem sempre gera uma solução que supre as exigências de desempenho do projeto.

Finalmente, os diferentes componentes reconfiguráveis são conectados no estágio de roteamento. Cada sinal é atribuído ao recurso de roteamento específico do *hardware* reconfigurável. Esta etapa pode tornar-se complicada caso não tenha sido realizada uma boa disposição dos blocos, pois sinais que percorrem distâncias maiores utilizam mais recursos. Um dos desafios de roteamento em FPGAs e sistemas reconfiguráveis é que os recursos de distribuição são limitados. Em geral o objetivo é minimizar o número de ligações (trilhas) utilizadas em um canal de comunicação entre unidades, mas estes canais devem ter a largura necessária para a computação. Entretanto, em sistemas reconfiguráveis, a quantidade de ligações é determinada no momento da fabricação. Assim, o roteamento de um FPGA concentra-se em minimizar o con-

gestionamento dentro das ligações disponíveis (BROWN et al., 1992b) (ALEXANDER; ROBINS, 1996) (CHAN; SCHLAG, 1997) (THAKUR et al., 1997) (NAM et al., 1999). Como o roteamento é uma etapa muito demorada, costuma-se verificar a viabilidade do mesmo antes da sua realização. Isto pode informar ao desenvolvedor se existe a necessidade de se alterar o projeto dos componentes reconfiguráveis (WOOD; RUTENBAR, 1997) (SWARTZ et al., 1998).

Cada uma das fases do projeto mencionadas anteriormente pode ser executada manualmente ou automaticamente usando ferramentas, como compiladores. Os compiladores de *hardware* para descrições de alto nível são cada vez mais utilizados para melhorar a produtividade no desenvolvimento de circuitos avançados em geral e projetos reconfiguráveis específicos.

As próximas seções apresentam métodos de projeto de alto nível sob duas perspectivas, de acordo com (TODMAN et al., 2005): projetos de propósitos específicos e projetos de propósitos gerais.

## 3.2 Projetos de Propósito Geral

Esta seção apresenta métodos e ferramentas de desenvolvimento de circuítos baseados em linguagem de propósito geral, como C, adaptadas para facilitar o desenvolvimento de *hardware*. Podemos incluir neste grupo as linguagens de descrição de *hardeware* VHDL (Apêndice A) e Verilog, que são amplamente usadas em plataformas comerciais.

Um número considerável de compiladores de C para *hardware* tem sido desenvolvido. Estes variam de compiladores que apenas visam gerar o *hardware* a outros que visam o desenvolvimento completo de sistemas *hardware/software*; alguns, ainda, realizam o particionamento entre *hardware* e *software*.

Este grupo pode ser subdivido em dois tipos de abordagens: de anotações e dirigido por restrições (*annotation and constraint-driven*) e compilação direta do código fonte. A primeira abordagem preserva o programa fonte em C ou C++ tanto quanto possível e faz uso de anotações e arquivos de restrições para guiar o processo de compilação. A segunda abordagem modifica a linguagem fonte para permitir ao desenvolvedor especificar características inerentes a sistemas reconfiguráveis, como por exemplo, a quantidade de paralelismo ou tamanho das variáveis a serem utilizadas.

#### 3.2.1 Abordagem de Anotações e Abordagem Dirigida por Restrições

Os sistemas mencionados a seguir empregam anotações no fonte-código e arquivos de restrições para controlar o processo de otimização. Geralmente, pequenas mudanças são suficientes para produzir um programa compilável, sem a necessidade de grandes reestruturações. Cinco métodos representativos desta abordagem são SPC (WEINHARDT; LUK, 2001), Streams-C (GOKHALE et al., 2000), Sea Cucumber (JACKSON et al., 2003), SPARK (GUPTA et al., 2003) e Catapult-C (MCCLOUD, 2004).

#### 3.2.1.1 SPC

Este método utiliza uma abordagem para geração automática de circuitos em *pipeline* otimizados, a partir de programas em alto nível, utilizando técnicas derivadas de compiladores que realizam vetorização de software. Isso envolve essencialmente a síntese de processadores *pipeline* que executam laços internos dos programas. Para tanto, é realizada uma análise de dependência similar à vetorização de *software*, que determina se pode ser gerado um *pipeline* para cado laço. Conseqüentemente, gera circuitos que exploram o paralelismo melhor do que outras ferramentas automáticas de desenvolvimento de alto nível. Baseada no *framework* SUIF (WILSON et al., 1994), esta abordagem usa transformações de laço e tira vantagem da reconfiguração em tempo de execução (*Runtime Reconfiguration - RTR*) e otimizações de acesso à memória.

Essa abordagem inclui ainda a síntese de circuitos não *pipeline* para laços, condições e sequências não-vetorizáveis. Podem ser utilizados dois modos: modo de *hardware* e modo de *codesign*. No modo de *hardware*, um processador é gerado para o programa inteiro, convertendo descrições de um programa sequencial em alto nível em linguagem de descrição de hardware (HDL). Na opção de *codesign*, partes do programa (tais como as partes não-sintetizáveis e as altamente irregulares) permanecem em software para serem executados no microprocessador principal. Este modo resulta em sistema de *hardware* e *software* em conjunto, com a geração automática de transferência dos dados e controle entre o microprocessador principal e o *hardware* reconfigurável.

#### **3.2.1.2** Streams-C

O método Streams-C (GOKHALE et al., 2000) compila programas C para VHDL sintetizável para um ou mais FPGAs assim como o controle *multi-thread* para o processador principal. Os alvos são aplicações baseadas em *streams*, cujas características podem ser ressaltadas: altas taxas de fluxo de uma ou mais fontes de dados; computação intensiva; acesso à memória local,

guardando coeficientes e outras constantes; sincronização ocasional entre fases do processamento.

A linguagem Streams-C é composta por um pequeno conjunto de anotações e bibliotecas utilizadas dentro de um programa C convencional. As anotações são utilizadas para declarar processos, *stream*, e sinais, e para indicar os recursos do FPGA. As bibliotecas são utilizadas para comunicação de dados entre os processos. Um processo pode ser executado no processador principal ou no FPGA. Para um processo no FPGA, o corpo do processo acessa apenas a memória local e deve ser escrito utilizando um subconjunto da linguagem C suportado pelo compilador Streams-C. Além disso, possui funções intrínsecas para manipular *stream* e sinais. Todas as declarações são inicializadas no início do programa e são mantidas até a subrotina termine.

O Streams-C utiliza o modelo de programação paralela de Comunicação entre Processadores Sequenciais (*Communicating Sequential Processes*) (CSP) (HOARE, 1978).

#### 3.2.1.3 Sea Cucumber

O método Sea Cucumber (SC) (JACKSON et al., 2003) gera programas para FPGAs a partir de programas em Java, utilizando um esquema similar ao Handel-C (CELOXICA, 2004) que será apresentado detalhadamente mais adiante. O SC aumenta o desempenho do sistema permitindo que o usuário particione o algoritmo comportamental em segmentos paralelos. Usando o suporte à concorrência, nativo do Java, estes segmentos paralelos são expressados como threads. SC gera um circuito final para cada thread em separado, gerando processos em hardware paralelo.

#### 3.2.1.4 **SPARK**

SPARK (GUPTA et al., 2003) é um *framework* de síntese de alto-nível que visa processamento de imagens e multimídia. Transforma uma descrição comportamental em ANSI-C em VHDL sintetizável. Compila o código em C utilizando as seguintes etapas: (a) cria uma lista especulativa para movimentação de código e transformação de laços; (b) realiza o controle de recursos com minimização de interconexões; (c) gera a máquina de estados finitos para o código fornecido; (d) realiza a geração de código produzindo código VHDL RTL sintetizável. Deve-se então utilizar uma ferramenta de síntese para sintetizar o código gerado.

O código C de entrada não possui nenhuma construção ou estrutura especial, entretanto SPARK não suporta alguns recursos da linguagem. São eles: ponteiros; recursão; saltos irregu-

lares (goTo); *break* e continue; aranjos multidimensionais; *structs*; e instruções do tipo (a ? b : c). SPARK utiliza técnicas de compiladores paralelos para melhorar o paralelismo em nível de instruções, incorporando idéias de operações mutuamente exclusivas, compartilhamento e custos de recursos de hardware. Entre estas técnicas pode-se ressaltar: desenrolamento de laços; fusão de laços; movimento de código; eliminação de sub-expressões comuns, eliminação de código morto; funções *in-lining*; e propagação de constantes.

#### **3.2.1.5** Catapult-C

Catapult-C (MCCLOUD, 2004) sintetiza uma descrição em C++ em nível de transferência de registradores (RTL), utilizando características da tecnologia. Usuários podem ajustar restrições para explorar melhor a utilização de espaço, controlar *pipeline* de laços e o compartilhamento de recursos.

## 3.2.2 Compilação Direta do Código Fonte

Uma abordagem diferente para adaptar a linguagem para a descrição explícita de paralelismo, comunicação e outras adaptações de recursos de *hardware*, como tamanho de variáveis. Como exemplos desse método de desenvolvimento pode-se apresentar ASC (MENCER et al., 2003), Handel-C (CELOXICA, 2004), Haydn-C (COUTINHO; LUK, 2003) e Bach-C (YAMADA et al., 1999).

#### 3.2.2.1 ASC

ASC (MENCER et al., 2003) é essencialmente uma biblioteca de C++ que pode ser compilada por um compilador C++ comum. O código ASC é, basicamente, um código C++ utilizando a biblioteca ASC para compilação. Quando compilado, o código ASC gera um código executável que age como um simulador no nível de bits (RTL) ou produz um circuito na forma de *netlist* de hardware.

Para os conceitos e descrições de tempo de *harware* utiliza tipos e operadores implementados como classes de C++. Isto permite ao usuário programar no nível desejado para cada parte da aplicação. A exploração Semi-automática de espaço permite um aumento adicional na produtividade do desenvolvimento, ao suportar processos de otimização em todos os níveis de abstração. O desenvolvimento orientado a objetos permite um eficiente reuso de código e inclui uma biblioteca integrada de geração de unidade aritmética (MENCER, 2002). Uma biblioteca

*floating-point* (LIANG et al., 2003) fornece mais de 200 unidades diferentes de ponto flutuante, cada uma com a largura de dados definida de acordo com a necessidade.

#### **3.2.2.2** Handel-C

Handel-C (CELOXICA, 2004) é baseada em um subconjunto de ANSI C com extensão para o suporte a computações paralelas e especifica recursos de *hardware* como largura de variáveis, manipulação de bits e canais de comunicação. Uma característica é que o sincronismo do circuito compilado é fixo em um ciclo por instrução de C. Isto permite que os programadores de Handel-C programem recursos de *hardware* manualmente.

Outra importante característica do Handel-C é que todas as contruções básicas (exceto E/S) são sintetizadas em hardware. Isso dá confiança ao desenvolvedor de que o desenvolvimento em Handel-C terá realmente o comportamento especificado.

Handel-C compila a uma máquina de estado *one-hot* usando um esquema de passagem de *token* desenvolvido por Page(PAGE; LUK, 1991). Numa máquina de estado *one-hot* cada atribuição do programa é mapeada em exatamente um flip-flop na máquina do estado. Estes flip-flops de controle capturam o fluxo do controle (representado pelo *token*) no programa: se o flip-flop de controle, que corresponde a uma atribuição particular, for ativo, o controle é então passado a essa atribuição e os circuitos compilados para essa atribuição são ativados. Quando a atribuição termina a execução, passa o *token* à atribuição seguinte no programa.

#### 3.2.2.3 Haydn-C

Haydn-C (COUTINHO; LUK, 2003) inclui características de Handel-C, VHDL e linguagens orientadas a objetos visando projetos baseados em componentes. Possui semântica similar a ANSI-C. Além disso, oferece suporte à explicitação de descrição de blocos paralelos, largura de bits variável, estruturas de FIFO *pipeline* e outras estruturas que permitem explorar características de *hardware*.

A inovação principal de Haydn-C é uma estrutura (*framework*) de anotações opcionais para a descrição de restrições e de transformações tais como programação e alocação de recurso. Existem transformações automatizadas de modo que um único projeto de alto nível possa ser usado para muitas execuções diferentes.

#### 3.2.2.4 Bach-C

Bach-C (YAMADA et al., 1999) é similar a Handel-C, baseado em ANSI-C com extensões que suportam especificação de paralelismo, comunicação e largura de dados. A semântica para paralelismo e comunicação é baseada em CSP e OCCAM (INMOS, 1988).

Circuitos desenvolvidos em Bach-C consistem de uma sequência hierárquica de *threads*, todas em paralelo e comunicação via canais sincronizados e variáveis compartilhadas.

A Tabela 1 apresenta os compiladores discutidos nesta seção, mostra a linguagem fonte e alvo e algumas possíveis aplicações de exemplo.

Tabela 1: Compiladores de propósito geral

| Compilador   | Linguagem Fonte      | Linguagem Alvo         | Aplicação Exemplo                  |

|--------------|----------------------|------------------------|------------------------------------|

| Streams-C    | C + Biblioteca       | RTL VHDL               | Alteração de Contraste em Imagens  |

| Sea Cucumber | Java + Biblioteca    | EDIF                   | nenhuma apresentada                |

| SPARK        | ANSI C               | RTL VHDL               | Preditor MPEG-1                    |

| SPC          | ANSI-C               | EDIF                   | Reconhecimento de padrão de string |

| ASC          | C++ usando classe de | EDIF                   | Encriptação                        |

|              | biblioteca           |                        |                                    |

| Handel-C     | Extensão de C        | VHDL Estrutural, Veri- | Processamento de Imagens           |

|              |                      | log, EDIF              |                                    |

| Handy-C      | Extensão de C        | Handel-C               | Filtro FIR                         |

| Bach-C       | Extensão de C        | VHDL Comportamental    | Processamento de Imagens           |

|              |                      | e RTL                  |                                    |

## 3.3 Projetos de Propósito Específicos

Com a grande variedade de problemas em que a computação reconfigurável pode ser aplicada, existem muitos domínios de problemas que merecem atenção especial, tais como: 1) processamento de sinais utilizando MATLAB, e 2) otimização de largura de dados.

Nesta seção será apresentada uma visão geral dos métodos para processamento digital de sinais e as ferramentas que visam a implementação reconfigurável. Será descrito então o problema de otimização de largura de dados, com as soluções que prometem trazer bons benefícios. Finalmente serão apresentados outros métodos de desenvolvimento de domínios específicos.

## 3.3.1 Processamento Digital de Sinais

Processamento digital de sinais (DSP) é uma das aplicações para a qual a computação reconfigurável tem sido mais aplicada e com mais sucesso. Isso pode ser percebido com a inclusão de blocos de *hardware* específicos para suporte a DSP pelos fabricantes de FPGAs

em seus *chips*. Tanto a Xilinx quanto a Altera (principais fabricantes de FPGA do mercado) já possuem uma ampla gama de *chips* com esses blocos, como as famílias Virtex-II, Virtex-II Pro, Virtex-4 e Virtex-5 pela Xilinx e Cyclone II, Stratix e Stratix II pela Altera.

Os problemas de DSP geralmente possuem as mesmas características: o tempo de desenvolvimento é geralmente pequeno e o tempo de processamento é alto; os algoritmos tendem a ser de cálculos numéricos intensos, com estruturas de controle muito simples; é aceitável um erro numérico controlado e métricas padrões são usadas para medir a qualidade da precisão.

Uma das principais ferramentas para desenvolvimento de aplicações DSP é o ambiente gráfico de programação Mathworks MATLAB Simulink (SIMULINK, ). Simulink é uma plataforma multidomínios de simulação e baseada em modelos para sistemas dinâmicos. Ela provê uma interface gráfica e um conjunto de bibliotecas customizáveis que pemite o desenvolvimento, simulação, implementação e teste de sistemas. O sistema é integrado com o MATLAB, provendo acesso a uma ampla gama de ferramentas para o desenvolvimento de aplicações, visualização e análise de dados e computações numéricas. A Xilinx possui o *System Genarator for DSP* (HWANG et al., 2001) que é o componente principal do Xilinx XtremeDSP, solução que combina o estado de arte de FPGAs, ferramentas de desenvolvimento, *cores* de propriedade intelectual, além de serviços de desenvolvimento e educacionais. A Altera possui o *DSP Builder* (ALTERA, 2006b) que é um sistema de desenvolvimento que faz a interligação entre o Quartus® II, ambiente de desenvolvimento da Altera, e o MathWorks MATLAB/Simulink.

## 3.3.2 Otimização da largura de dados

Nos microprocessadores convencionais a largura em bits dos dados é definida a *priori* pela arquitetura do processador e não pode ser alterada. Na computação reconfigurável o tamanho de cada variável pode ser definido com o objetivo de obter o melhor resultado de tamanho do projeto, velocidade, consumo de energia e qualidade numérica do resultado. O uso de tamanho de dados customizado é um dos pontos fortes e principais da computação reconfigurável.

Devido a essa flexibilidade é desejável automatizar o processo de encontrar a melhor representação possivel para o tamanho das variáveis. Tem sido discutido, frequentemente, que a implementação em *hardware* mais eficiente de um algoritmo é aquela que utiliza uma grande variedade de precisões para representar os diferentes tamanhos das diferentes variáveis internas (CONSTANTINIDES et al., 2001).

Em (CONSTANTINIDES; WOEGINGER, 2002) foi demonstrado que o problema de otimização de tamanho de variável é NP-hard (*Non-deterministic Polynomial-time hard* - uma classe

de complexidade de problemas que podem ser resolvidos por uma máquina de Turing não determinística em um tempo polinomial), até mesmo para sistemas com propriedades matemáticas especiais que simplificam o problema por uma perspectiva prática (CONSTANTINIDES et al., 2003). Existem, entretanto, muitas abordagens publicadas para resolver o problema da otimização do tamanho de dados. Estes podem ser classificados como heurísticas que oferecem uma melhor razão área/sinal (CONSTANTINIDES et al., 2001) (KUM; SUNG, 2001) (WADEKAR; PARKER, 1998), abordagens que fazem suposições nas simplificações nas propriedades de erro (KUM; SUNG, 2001) (CANTIN et al., 2001), ou abordagens que podem ser aplicadas a algoritmos com propriedades matemáticas particulares (CONSTANTINIDES et al., 2002)

Alguns trabalhos publicadas sobre o problema de otimização de tamanho de dados usam uma abordagem analítica que escalona a estimação de erro (WADEKAR; PARKER, 1998) (NAYAK et al., 2001) (STEPHENSON et al., 2000), alguns usam a simulação (KUM; SUNG, 2001) (CANTIN et al., 2001), e alguns usam um híbrido dos dois (CMAR et al., 1999). A vantagem das técnicas analíticas é que não requerem uma simulação da representação dos estímulos e podem ser mais rápidas; entretanto, elas tender a ser mais pessimísticas.

#### 3.3.3 Outros métodos de desenvolvimento

Além de processamento de sinais, processamento de vídeo e imagem são outras áreas que se beneficiam muito com métodos específicos de desenvolvimento. Três exemplos seguintes mostrarão isso. Além disso, trabalhos recentes indicam que uma outra área que tem se beneficiado muito é a de redes de computadores. O exemplo de implementação de *firewall* em *hardware* ilustrará essa afirmação.

#### **3.3.3.1 CHAMPION**

CHAMPION (ONG et al., 2001) é um ambiente de desenvolvimento completo que possui as ferramentas necessárias para capturar, simular e implementar aplicações para plataformas reconfiguráveis múltiplas. Ele mapeia aplicações desenvolvidas no ambiente gráfico de desenvolvimento Cantata, onde todas as aplicações são desenvolvidas usando funções ou módulos pré-desenvolvidos chamados *glyphs*. O CHAMPION então realiza a sincronização dos dados utilizando para isso *buffers* de atraso. Após a sincronização dos dados é realizado o particionameno mantendo o fluxo funcional do sistema, dividindo o sistemas em vários *netlists* que devem ser sintetizados e configurados nos componentes de *hardware* correspondentes.

#### 3.3.3.2 IGOL Framework

IGOL (*Imaging and Graphics Operator Libraries*) (THOMAS; LUK, 2002) é um sistema implementado em camadas que permite um fácil desenvolvimento, teste e execução de hardware acelerador. O *framework* também suporta o desenvolvimento utilizando a linguagem Handel-C. O IGOL é baseado no Microsoft *Component Object Model* (COM) para o desenvolvimento de componentes. Isso permite que sejam desenvolvidos *plug-ins* para serem incorporados a vários aplicativos do sistema operacional Windows, como Premiere, Winamp, VirtualDub e DirectShow.

#### 3.3.3.3 SA-C

SA-C (*Single Assignment C*) (NAJJAR et al., 2003) é uma variante da linguagem C criada para automatizar a compilação de algoritmos escritos em linguagem de programação em sistemas reconfiguráveis baseados em FPGAs. Uma das principais características desta linguagem é que as variáveis só podem ser atribuídas uma vez, quando da sua declaração. O SA-C possui também arranjos multidimensionais, incluindo arranjos em que o tamanho não é conhecido em tempo de compilação. Destaca-se entre esses arranjos o elemento janela (*window*), que possui funções adaptadas para ele, como o *for*.